电路运行图 1 显示了耦合电感的基本 SEPIC。当FET (Q1) 开启时,输入电压施加于初级绕组。由于绕组比为 1:1,因此次级绕组也被施加了一个与输入电压相等的电压;但是,由于绕组的极性,整流器 (D1) 的阳极被拉负,并被反向偏置。整流器偏颇关闭,要求输出电容在这种“导通”时间期间支持负载,从而强迫 AC电容 (CAC) 充电至输入电压。Q1 开启时,两个绕组的电流为 Q1 到接地,而次级电流流经 AC 电容。“导通”时间期间总 FET 电流为输入电流和输出次级电流的和。

FET 关闭时,绕组的电压反向极性,以维持电流。整流器导电向输出端提供电流时,次级绕组电压现在被钳位至输出电压。通过变压器作用,它对初级绕组的输出电压进行钳位。FET 的漏极电压被钳位至输入电压加输出电压。FET“关闭”时间期间,两个绕组的电流流经 D1 至输出端,而初级电流则流经 AC 电容。

伏-微秒平衡耦合电感由两个非耦合电感代替时,电路运行情况类似。要让电路正确运行,必须在每个磁芯之间维持伏-微秒平衡。也就是说,对于两个非耦合电感而言,在FET“导通”和“关闭”时间期间,每个电感电压和时间的积必须大小相等,而极性相反。通过代数方法表明,非耦合电感的 AC 电容电压也被充电至输入电压。在 FET“关闭”时间期间,输出端电感被钳位至输出电压,其与耦合电感的次级绕组一样。在 FET“导通”时间期间,AC 电容在电感施加一个与输入电压相等但极性相反的电势。每间隔时间,对电感定义电压进行钳位,这样伏-微秒平衡便决定了占空比 (D) 的大小。其在连续导通模式 (CCM) 运行时,可简单表示为:

FET 导通时,施加于输入端电感的电压等于输入电压。FET关闭时,伏-微秒平衡通过钳位其 VOUT 来维持。记住,FET 导通时,输入电压施加于两个电感;FET 关闭时,输出电压施加于两个电感。两个非耦合电感 SEPIC 的电压和电流波形,与耦合电感版本的情况非常类似,以至于很难分辨它们。

两个还是一个?

如果 SEPIC 类型之间确实存在少许的电路运行差异的话,那么我们应该使用哪一种呢?我们通常选择使用耦合电感,是因其更少的组件数目、更佳的集成度以及相对于使用两个单电感而言更低的电感要求。然而,高功率现货耦合电感有限的选择范围,成为摆在广大电源设计人员面前的一个难题。如果他们选择设计其自己的电感,则必须规定所有相关电参数,并且必须面对更长的交货时间问题。耦合电感 SEPIC 可受益于漏电感,其可降低 AC 电流损耗。耦合电感必须具有 1:1 的匝数比,以实施伏-微秒平衡。选择使用两个单独的非耦合电感,一般可以更广泛地选择许多现货组件。由于并不要求每个电感的电流和电感完全相等,因此可以选择使用不同的组件尺寸,从而带来更大的灵活性。

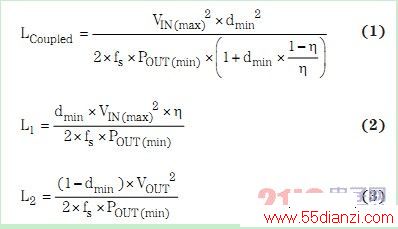

方程式 1 到 3 表明了耦合电感和非耦合电感的电感计算过程。

实例设计

“表 1”所示规范为设计比较的基础。第一个设计使用一个耦合电感,而第二个则使用两个非耦合电感。

参数

www.55dianzi.com

图 3 SEPIC 原型

SEPIC 电路具有非常复杂的控制环路特性,同时由于分析结果的解释一般较为困难,因此必需使用一些数学工具来进行具体分析。添加这种 R/C 阻尼滤波器(220 µF/2Ω)会增加成本、电路面积和损耗。相比一个单耦合电感,使用两个非耦合电感会使面积增加 10%。

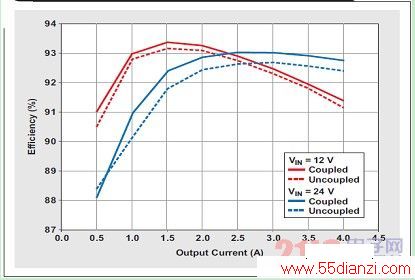

图 4 显示了两种电路的测量效率。我们可以看到,耦合电感设计的效率增加多达 0.5%。这可能是由于耦合电感设计的总铁芯损耗更低,因为其 DC 接线损耗实际高于使用非耦合电感的设计。L2 使用一种粉状铁芯材料,其往往具有比L1 和自定义 Renco 耦合电感所用铁氧体材料更高的损耗。尽管使用了 L2 的铁氧体材料,但其会导致更大的面积。

结论

利用一个耦合电感或者两个非耦合电感,均能成功实施SEPIC。更高的效率、更小的电路面积以及更良性的控制环路特性,这些都是使用正确缠绕的自定义耦合电感时原型硬件所带来的好处。自定义组件没有现货器件那么理想,而许多耦合电感随处可以购买到,且尺寸更小。如果产品上市场时间至关重要,则非耦合电感可为设计人员带来更大的灵活性。

图 4 耦合和非耦合电感均获得了较好的效率

本文关键字:转换器 元器件特点及应用,元器件介绍 - 元器件特点及应用

上一篇:AD7192在电子秤系统中的应用