近年来,采用高分辨率的∑-Δ型数据转换器颇为流行。它的个突出优点是在1片混合信号CMOS大规模集成电路上实现了过采样与数字信号处理技术的结合。这一技术的显著优点:高精度高分辨率,其分辨率高达24位。目前,∑-Δ型的DAC可实现24位的数模转换,但是20位以上的DAC都是为音频系统服务的,如Analog公司的AD18系列、Burr-Brown和TI公司的PCM17系列、Crystal公司的CS4930等。这些半导体公司生产的高精度24位的DAC都是音频DAC芯片。这些芯片必须满足音频的采样频率、数据输入格式、声道选择等条件。这些条件的限制使得高分辨率的音频DAC只能应用于音频系统中,如果需要高精度的通用DAC作为软换器(例如:我们设计的高速高分辨率模数转换系统需要24位DAC作为校准的基准),只能在现有音频DAC基础上进行改造。通过外围电路扩展和程序设计,可实现通用DAC的时钟信号的改造、数据转换模式的改造、采用频率的改造等,满足通用DAC系统的要求。

本文以Burr-Brown公司推出的PCM1748为例,说明音频DAC器件的改造方案。PCM1748是CMOS立体声集成电路。它采用TI公司的增强型多级∑-Δ结构和噪声整形技术,执着16~24位的工业标准音频数据以及三线串行控制端口操作,最高采样率可达100kHz。

2 音频DAC的工作原理

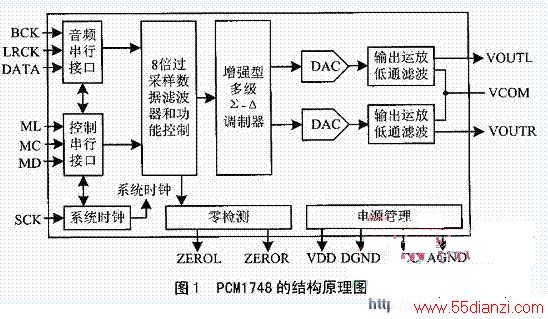

高分痃率音频DAC大都采用多级幅度量化高阶∑-Δ调制器结构中。这样,在实际应用中可以提高音频动态范围,减小时时钟抖动的敏感度,降低由此引发的失真;内置过采样的数字滤波器具有2种可供选择滚降特性:慢滚降和陡滚降。对于PCM1748,其内部是采用8级副度量化和4级噪声整形技术。8级调制器结构具有更的稳定性和抗抖动能力。过采样调制器和内插滤波器的采样率是64fs。图1是PCM1748的结构图。

BCK:音频数据位时钟;

DATA:音频数据输入;

LRCK:左右声道音频数据的锁存;

以上3个引脚都是数字逻辑,耐压能力5V。

ML:模式控制锁存输入;

MC:模式控制数据输入;

SCK:系统时钟输入;

ZEROL、ZEROR:左右声道零标志位;

VDD、DGND:数字电源;

VCC、AGND:模拟电源;

VOUTL:VOUTR:左右声道模拟输出;

VCOM:公共端。

PCM1748在正常供电电源下,是通过串行接口来送入数据和进行控制的。它的串行接口包括音频三线同步串行接口和控制三线异步串行接口。

频串行接口包括LRCK、BCK、DATA。其中,BCK是串行音频位时钟。它的功能是将DATA上现有的数据通过此时钟作用送入音频接口的移位寄存器内,并且注意串行数据是在BCK的上升沿送入音频接口的。LRCK是串行音频接口在左/右声道数据字锁存时钟。它的功能是将数据锁存到接口内部的移位寄存器中。这里应当注意,无论BCK还是LRCK都应当与系统时钟SCK同步,因而最好LRCK和BCK应从系统时钟SCK获取。同时,LRCK与采样频率fs一致。BCK可选择为32、48或64倍的采样频率。PCM1748支持工业标准的音频数据格式,包括标准格式、I2S格式和左对齐格式。格式选择是通过控制寄存器来设置。所有格式都需要二进制补码,高位在前的音频数据,如图2所示左对齐格式及其操作时序。

PCM1748具有用户可编程的模式控制。这些可控模式是通过串行控制口送入控制字来设置的。具体的可控模式功能有:软静噪、过采样率、DAC操作控制、音频数据格式、输出相位选择等。相应的寄存器认状态和控制寄存器地址、定义,可参考说明书。

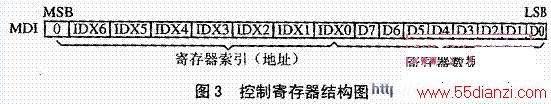

控制串行接口是通过对片上的模式寄存器进行编写来实现控制功能的。其中MD是串行数据输入,用来写模式寄存器;MC是串行位时钟,用来将数据控制口;ML是控制口的锁存时钟,是将控制字锁存到寄存器中。所有的串行控制口的写操作都是采用16位数据字,如图3所示。其中最高位为0;IDX[6~0]是标志位,它为写操作提供寄存器索引或地址,低7位D[7~0]是写放到该地址的寄存器数据值。图4表明这一写入时序。

通过串行口的正确控制及特定音频数据的输入,在音频特定采样频率及时钟控制下,再辅以必要的外围电源和输出电路,PCM1748就可以正常地进行音频数据转换了。

3 将音频DAC改造为通用

在保证音频DAC正常工作的前提下,将其改造成为通用型DAC的设计,要是要突破音频信号的数据格式和采样频率的限制,使其适应通用数据转换器的使用。为实现这一功能,我们采用TI公司的TMS320F206(简称F206)作为控制的核心器件,需要从以下几方面进行设计。

(1)电源的设计

音频DAC正常工作的电源包括模拟电源和数字电源。模拟电源VCC采用+5V供电,提供DAC模拟和输出滤波器的电源;数字电源VDD采用3.3V供电,提供数字滤波器和串行接口的电源。为减少电源数量,采用美信公司的DC-DC转换芯片MAX1748将+5V转换为3.3V,同时,系统中滤波和输出电路的运放需要-5V的电源,也可通过MAX735将+5V转换而得,如图5所示。

2)时钟信号的设计

对于时钟的设计主要包括音频串行时钟的设计和控制串行时钟的设计2部分(见图5)。

音频串行时钟主要是BCK、LRCK、还有系统主时钟SCK。这里LRCK等于采样频率fs,BCK采用64fs。为设计简单,我们利用F206的CLKOUT1(20MHz)作为SCK,提供系统时钟,利用分频器件74HC393的256分频作为LRCK,4分频作为BCK。这样采样频率确定为20MHz/256=78.125kHz。通过不同的分频比可以确定不同的采样频率。

控制串行接口的时钟ML、MC可直接由F206的同步串口时钟CLKX和FSX提供。

由于BCK和MC都是利用F206的同步串口时钟线CLKX,为区分音频串行接口的数据和控制串行数据,BCK-CLKX和MC-CLKX采用模拟开关74HC251控制。需要送控制字时,将MC与CLKX接通;需要送数据时,将BCK与CLKX接通,并且通过8255扩展的I/O口进行74HC393和74HC251的触发和切换。

(3)数据的写入

音频串行口的数据输入DATA与F206的同步串行口DX相连,也就是数据由同步串口提供。F206采用连续模式下外部时钟方式。74HC393的4分频输出连至PCM1748的BCK和F206的CLKX。这里F206应设置同步串口寄存器SSPCR,采用CLKX外部时钟源。由于F206在CLKX上升沿发送数据,为保证数据的可靠传输,应设置SSPST改变CLKX极性,下降沿发送数据。这里,我们采用的是24位左对齐的数据格式。F206检测到LRCK的下降沿一定时间后开始传送数据,每次传送2个字。根据左对齐的方式只截取高24位作为需要的24位数据。这里需要说明的是,24位数据采用的是二的补码格式。

本文关键字:转换器 元器件特点及应用,元器件介绍 - 元器件特点及应用

上一篇:可控硅在红外遥控开关的应用