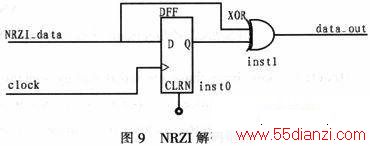

4.2 NRZI解码器设计

NRZI解码器设计是NRZI编码器的逆过程。图9为本设计采用的NRZI解码电路。其中,DFF为D触发器,XOR为异或门。NRZI_data为信号输入端,数据来自经光纤传输的NRZI码;cLOCk时钟频率同编码起时钟频率,即为NRZI_data码元速率的2倍(由FPGA倍频电路实现);data_out为解码器输出。

NRZI解码器ModelSim仿真波形如图10所示。NRZI_data输入数据分别为D30.0和D7.1编码后的数据。

上一篇:UHF平衡功率放大器设计及优化