3.2 车电总线接口设计

3.2.1 CAN总线接口设计

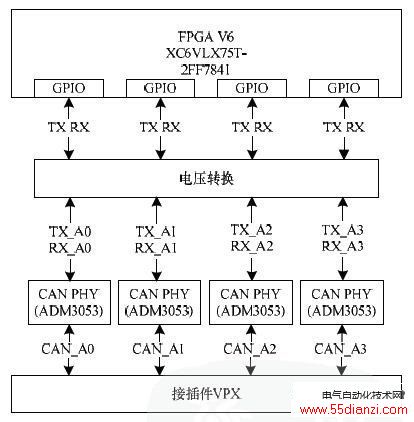

单元模块通过FPGA输出四路GPIO信号,GPIO连接电压转换芯片以完成电平转换,CAN总线信号完成电平转换后连接CAN芯片,从而输出CAN总线信号与总线接口单元VPX接插件相连,如图7所示。

图7 CAN总线接口硬件组成原理

CAN帧时,处理器驱动在内存定义并组织一个下图结构体,使用RapidIO中NWRITE-R事务,写入FPGA控制器CAN发送缓冲区地址,即刻完成发送;当CAN控制器完成发送后,将对该处理器产生中断,告知发送结果。

上一篇:识别计算机串口的COM号的方法