1.5Memory总线信号完整性分析

设计线宽5mil,阻抗51.3ohm。

1.5.1Memory总线时钟信号

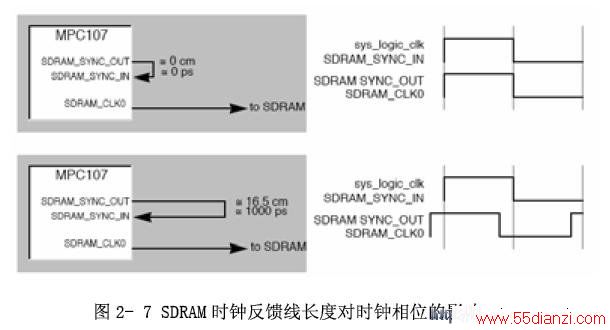

Memory总线时钟信号由MPC107给出。MPC107提供4个时钟信号:SDRAM_CLK(0:3),这些时钟信号能驱动一个或更多的器件。MPC107可以通过数字锁相环(DLL)来控制这些时钟信号,DLL能用于调整时钟和控制及数据信号的相位关系。时钟相位调整可用来对重负载的Memory总线提供补偿,或者用来补偿不能满足MPC107的Memory总线时序关系的SDRAM器件。通常的调整方法是调整MPC107的外部时钟反馈线(SDRAM_SYNC_OUT到SDRAM_SYNC_IN)的长度。

图2-7展示了不同长度反馈线对时钟信号相位关系的影响。

注:sys_logIC_clk是MPC107的内核时钟,等价于SDRAM_SYNC_IN。

设计Memory时钟反馈线长度与SDRAM芯片的时钟线等长,同时由于反馈线和时钟线都是只有一个负载,所以MPC107内部Memory控制逻辑时钟和SDRAM接收时钟相位基本相同。

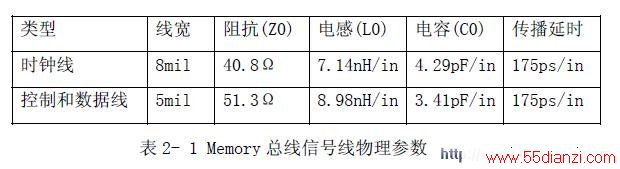

1.5.2Memory总线信号时序关系验证

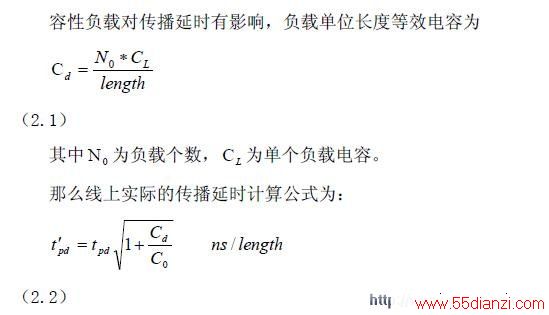

根据整板的层叠结构图以及信号线的宽度,得到Memory总线信号线的一些参数如表2-2所示。类型线宽阻抗(Z0)电感(L0)电容(C0)传播延时时钟线8mil40.8Ω7.14nH/in4.29pF/in175ps/in控制和数据线5mil51.3Ω8.98nH/in3.41pF/in175ps/in

表2-1Memory总线信号线物理参数

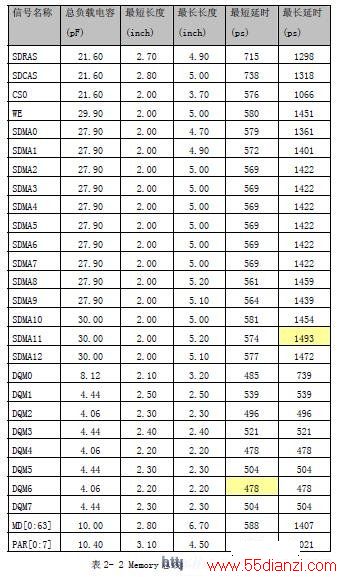

各Memory信号的延时如表2-3所示,其中“最短长度”是同一个网络上距离MPC107最近的负载与MPC107上相应点的布线距离,“最长长度”是距MPC107最远的负载与MPC107上相应点的布线距离。

表2-3不包括时钟信号,SDRAM_CLK(0:3)的布线长度以及SDRAM_SYNC_OUT到SDRAM_SYNC_IN的布线长度都为2inch,等长,不影响Memory信号的时序分析。

表2-2Memory总线信号延时计算

表中,最短飞行时间为478ps,最长飞行时间为1493ps。

下面是100MHz频率下Memory信号的时间富裕量分析。

表2-3Memory总线信号时序分析

可以看出,在最坏情况下,信号“建立时间”有857ps的富裕量,完全能满足Memory信号时序要求。因为MPC107的信号有效时间为5.5ns,所以信号“立时间”和“保持时间”都能够满足要求。

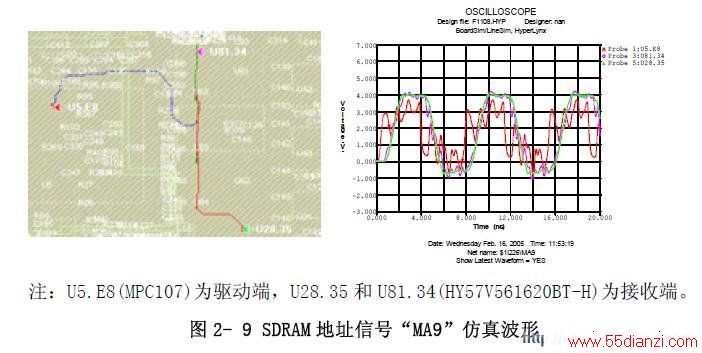

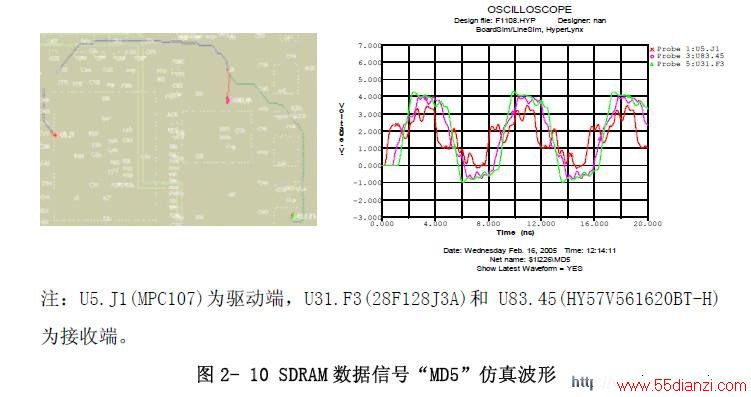

1.5.3Memory总线信号仿真

Memory总线CLK信号采用源端阻抗匹配策略,提高信号质量,减小时钟信号反射。图2-8到图2-10列出了Memory的典型CLK信号、地址信号、数据信号、控制信号的PCB走线图以及在 HyperLynx 仿真软件 的BoardSim工具下的仿真波形,PC107和SDRAM芯片的IBIS模型均来自于芯片厂商(Motorola和Hynix)

1.6PCI总线信号完整性分析

板上有两条PCI总线:PCI0为 32bit@33MHz ,PCI1为 64bit@66MHz 。

设计线宽5mil,特征阻抗为51.3ohm。

1.6.1PCI总线时序参数

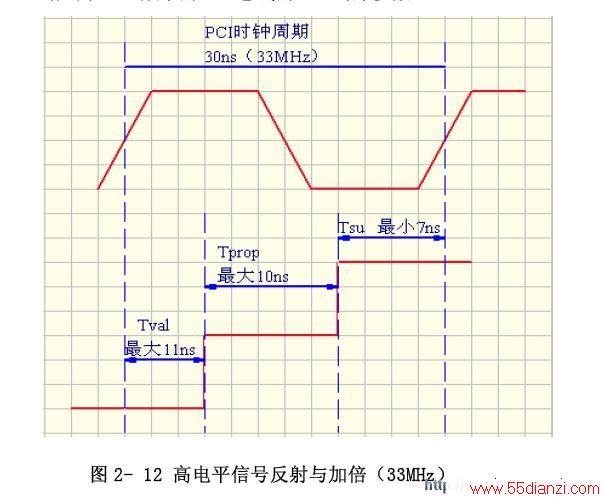

在PCI总线信号的电气特性上,不采用端接技术,而是利用信号的反射。采用经过仔细选择、相对弱的输出驱动器,部分地驱动信号线到期望的逻辑状态,一般情况下,驱动器仅驱动信号达到期望逻辑电压的一半。

当信号延PCB线向前传输并到达线的末端时,发生反射并且信号电压幅度加倍。在返回过程中再次通过每个设备,每个设备的输入就有了一个有效的逻辑电压。最后,返回到源端的波被驱动器内部的阻抗所吸收。利用这一方法,驱动器的尺寸和浪涌电流减半。注意信号反射发生在相邻的时钟上升沿之间,在时钟信号的上升沿每个设备的输入已经达到稳定状态。

图2-12给出了33M频率的PCI总线的一些时序参数。

有3个参数与PCI信号时序有关:

Tval(输出有效时间):设备总是在PCI时钟的上升沿开始驱动信号,Tval是时钟上升沿到信号有效输出的延时时间。驱动器必须保证其输出电压尽早稳定,从而保证在时钟的下一个上升沿接收端检测到有效的逻辑电平。33M的PCI信号的输出有效时间规定为最大11ns,66M下为6ns。

Tprop(传输延迟时间):信号从源端输出,传播到终端并反射(电压加倍)回源端所需时间。33M的PCI信号的传输延迟时间规定为最大10ns,66M下为5ns。

Tsu(建立时间):在时钟的下一个上升沿(所有接收设备采样其输入)之前,信号在所有输入上都必须稳定在最后状态所需的最短时间。33M的PCI总线的REQ#的建立时间是12ns,GNT#的建立时间是10ns,其它信号的建立时间是7ns;66M的PCI总线的REQ#和GNT#的建立时间是5ns,其它信号的建立时间是3ns。

Th(保持时间):信号在采样点(即时钟上升沿)后必须保持其当前逻辑状态的一段时间。PCI信号的保持时间规定为0ns。

1.6.2PCI总线布线及时序关系验证

对于PCI总线信号的布线,主要考虑三点:传输线阻抗;布线拓扑结构;信号线长度。

(1)传输线阻抗。布线应满足PCI规范的阻抗要求,并且有较好的一致性。

(2)布线拓扑结构。采用菊花链式的布线拓扑较为理想,星型拓扑或混合拓扑结构由于信号分叉较多,信号质量不好。

(3)信号线长度。因为信号的Tval、Tsu等时间参数由芯片本身决定,在布线上能控制的时序参数只有Tprop。信号线的长度将决定Tprop是否满足要求。

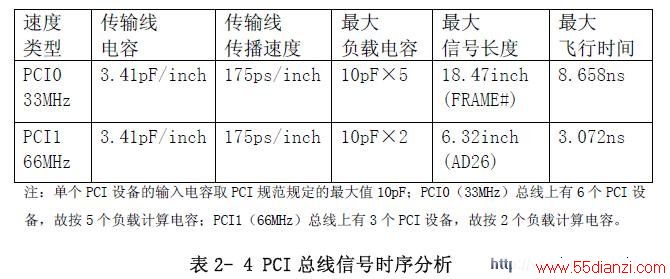

表2-5列出了PCI总线信号(不包括时钟信号)与传输速度相关的数据。

注:单个PCI设备的输入电容取PCI规范规定的最大值10pF;PCI0(33MHz)总线上有6个PCI设备,故按5个负载计算电容;PCI1(66MHz)总线上有3个PCI设备,故按2个负载计算电容。

表2-4PCI总线信号时序分析

PCI0总线信号的最大飞行时间为8.658ns,小于PCI规范的传播延时最大10ns(33M频率)的限制,满足Tprop要求。

PCI1总线信号的最大飞行时间为3.072ns,小于PCI规范的传播延时最大5ns(66M频率)的限制,满足Tprop要求。

1.6.3PCI总线信号仿真

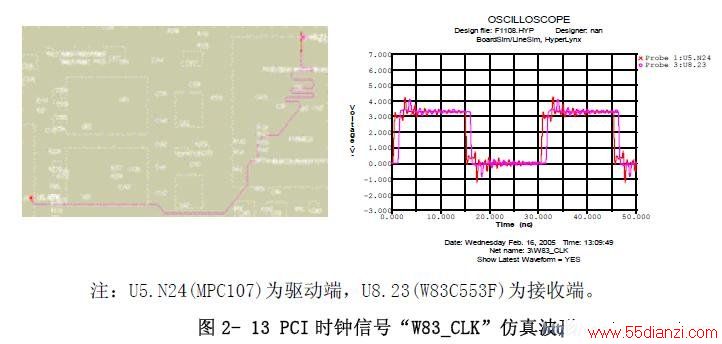

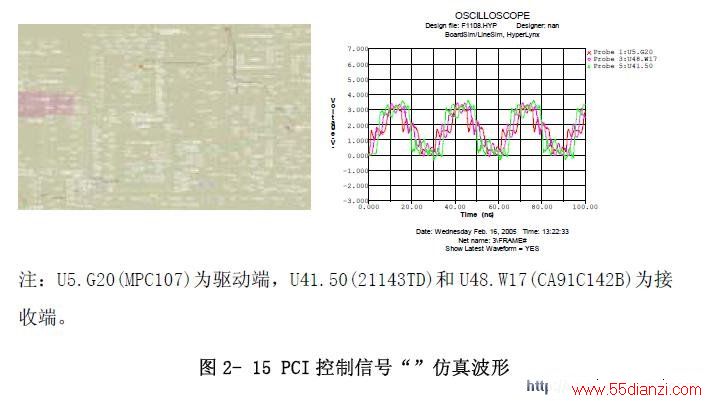

同Memory信号的时钟一样,PCI时钟线也采用源端串联匹配。根据信号仿真结果,取33Ω的串联电阻。下面是一些典型时钟线、地址数据线和控制线的PCB走线情况和仿真结果。

2.7总结

从上面的信号仿真波形就可以看出,通过设计合理的层叠结构、传输线阻抗、阻抗匹配以及布线拓扑结构,对于几百兆赫兹的信号而言一般都不会存在信号完整性问题。

因为传输线存在传输延迟,对高速信号,特别是总线信号而言,满足信号的时序关系是至关重要的。如果时序关系有问题,信号质量再好也没用。根据总线信号时序要求和芯片数据手册,事先要计算设计各种信号线的合理长度范围,PCB布局布线时以计算好的信号长度为依据,合理控制时钟线、控制信号线以及地址数据线的走线长度,PCB布线完成后最后再次计算验证时序关系是否满足。信号完整性和满足时序关系是逻辑电路功能物理实现的必要保证。

本文关键字:仿真软件 综合-其它,单片机-工控设备 - 综合-其它