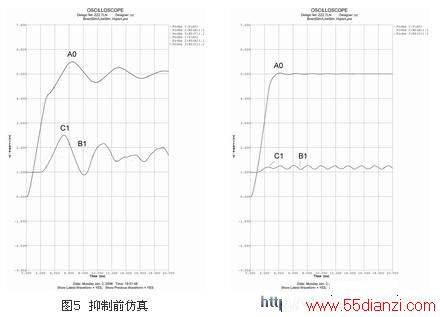

该基本模型有两个网络:驱动器A0(驱动线路为时钟信号线,其工作频率为5.12MSPS),通过传输线连接到1MW的电阻C0上;接收模式的驱动器A1,通过传输线连接在720KW的电阻C1上。每一条被耦合的传输线的特征阻抗都是68.8W,耦合长度是9in。HyperLynx计算出每条线上的延时大约是1.581ns。模型分为8层,设定两个信号线都为内层线(及微带线)且为同层。在PCB布局布线约束条件中,线宽为5mil,线间距为5mil,相对介电系数设置为4.3。图中分别在A0、B1、C1处加上了示波器探头,可利用示波器观看波形,B1的10MW电阻也是为了加探头而设置的。仿真结果如

www.55dianzi.com

图5所示。

串扰的抑制

不管是设计前的串扰计算,还是布局布线前的仿真,或是布局布线后的仿真,都是为了使 PCB 板能快速达到最小的干扰。因此需要在设计过程中运用以前的经验来解决现在的问题,以下就是有效避免布局布线中串扰的经验总结:

1)容性耦合和感性耦合产生的串扰随受干扰线路负载阻抗的增大而增大,所以减小负载可以减小耦合干扰的影响;

2)尽量增大可能发生容性耦合导线之间的距离,更有效的做法是在导线间用地线隔离;

3)在相邻的信号线间插入一根地线也可以有效减小容性串扰,这根地线需要每1/4波长就接入地层。

4)感性耦合较难抑制,要尽量降低回路数量,减小回路面积,不要让信号回路共用同一段导线。

5)避免信号共用环路。

在 高速 PCB设计的过程中,不仅需要对理论概念的详细理解,同样需要不断的积累经验,不断完善理论。同时,对相关辅助软件的熟练运用也可以缩短设计周期,从而提高竞争力,对设计的成功完成起到重要的作用。

结语

高速PCB板级、系统级设计是一个复杂的过程,包括信号串扰在内的信号完整性问题越来越不容忽视,因此需要设计者在设计的时候对信号完整性问题有全面的规划与考虑,在设计周期的各个阶段采用不同的方法来确保设计快速、精确地完成,从而节约时间、避免重复。

本文关键字:暂无联系方式综合-其它,单片机-工控设备 - 综合-其它