图7. 交易级协同仿真情境的范例。

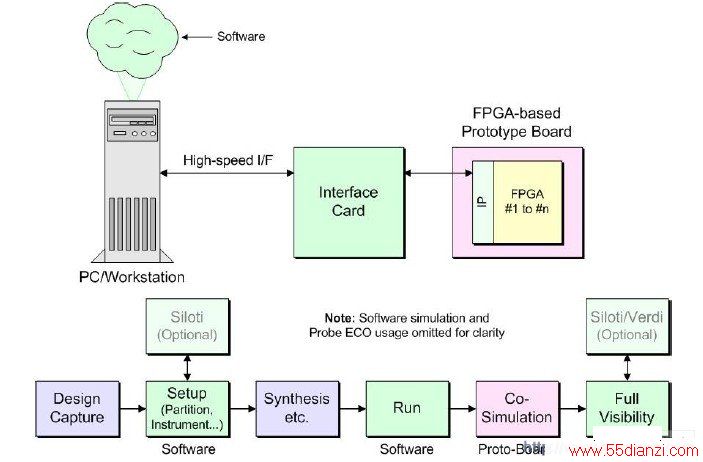

最后,让我们看看HDL协同仿真,这种加速验证流程,其速度比单仅使用软件仿真要快上数十倍。同样地,testbench (或许是设计的一部份) 常驻在工作站上,而大量 (或全部) 设计被加载到原型板。在这个情境中,工作站上执行的软件会自动分割设计,建立原型板,和产生可供软件仿真器连接的包装器(wrapper)。执行时,软件会控制原型板与ModelSim、NC或VCS等业界标准软件仿真器之间的协同仿真互动。如同前面几个情境中的讨论一般,透过软件与FPGA内部技术的组合,可在特定时间或按照逐一频率周期,将原型板上FPGA内部状态的能见度,包括寄存器与内存输出,如图8所示。

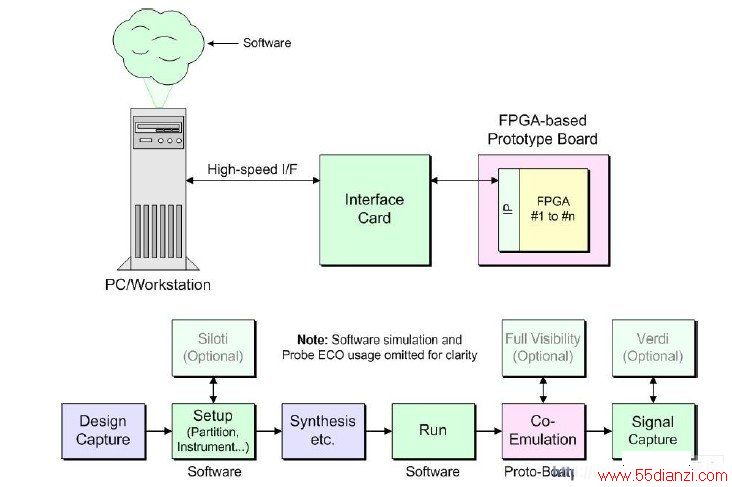

图8. HDL协同仿真情境的范例。

新一代原型验证平台的优点

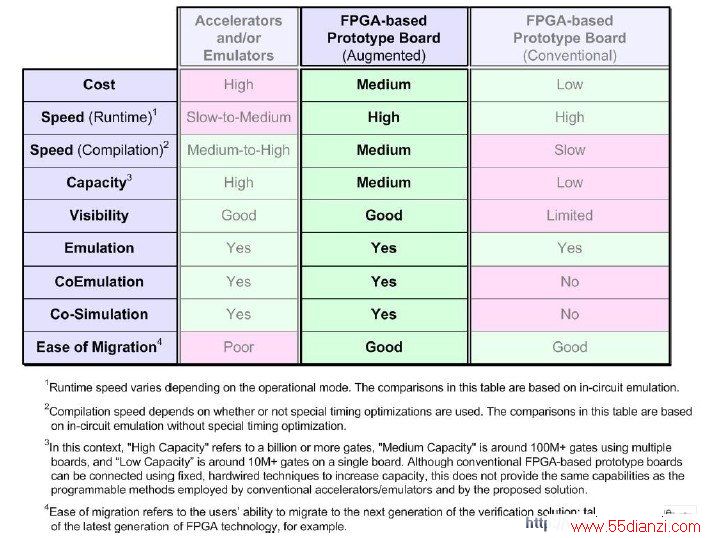

产品在市场上的存活时间及上市前置时间不断缩短造成了当今SoC设计与验证团队的莫大压力。软件仿真提供对设计内部的100%能见度,但是只适合于设计的一小部分,或者整个设计的数十个频率周期而已。然而,完全验证现代SoC需要耗费成千上万甚至百万频率周期,所以需要某种形式的硬件辅助验证。各式各样的硬件辅助验证解决方案具备不同的功能、优点与弱点。表1提供了各种硬件辅助验证技术的大略比较。

传统硬件加速器与仿真器提供大容量、相对快速的编译时间,以及相当良好的设计能见度。然而,这些系统太昂贵而难以广泛运用,而且因为转移成本高昂,也难以与时俱进地升级至新一代解决方案。比较上,传统FPGA式原型板提供高效能,而且比较便宜;但是,缺乏设计能见度与精密的侦错功能,无法克服当代SoC的复杂度,而且通常仅以硬件仿真模式来运用。

表1. 硬件辅助验证技术的比较。

为了解决这些问题,我们建议一种SoC验证的新方法,将传统FPGA式原型板转变成桌上型加速器/仿真器。这需要创新的互连技术,能够提供对预制与定制设计板的通用连结;还有特殊化的软件自动化,在工作站上以硬件仿真、协同仿真模式执行,并具备极高的设计能见度。

运用强化上述功能的FPGA式原型板,SoC开发人员可快速验证个别模块 (包括内部与第三方IP模块) 和设计模块是否正常运作,甚至于整个SoC设计的验证。这个新一代原型验证平台可提高FPGA式原型版的投资报酬率及生产力,提供更高验证效率与弹性,并能快速转移到配备最新FPGA技术的原型板。

本文关键字:暂无联系方式EDA/PLD技术,单片机-工控设备 - EDA/PLD技术