2. 3. 4 混合模块

该模块由数据缓冲寄存器(AdderBuf)和加法器(Adder)两部分组成。数据缓冲寄存器读取控制端口( Sel)的状态,然后判断各个输入是否有效,即是否送入到输出端口。若某输入端口有效,则将该端口数据直接送入加法器;若无效则送出数据0。

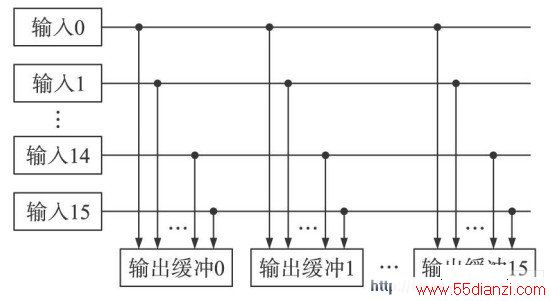

2. 3. 5 交换矩阵模块

交换矩阵的工作原理是一个16转256的 分配器 ,将每一路输入分配为16路,分别送入每一路输出的混合模块中。其结构如图6所示。

图6 交换矩阵模块结构图。

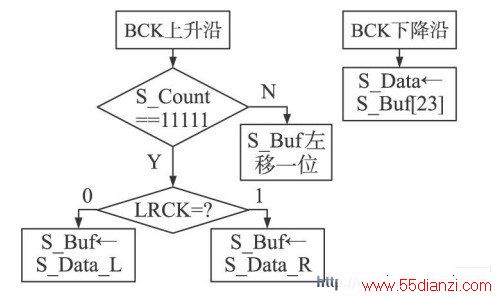

2. 3. 6 输出并/串转换模块

该模块负责将混合模块输出的24 bit并并行数据转化为PCM1681能够接收的串行PCM编码。数据传输格式与PCM4204相同。模块内部建立一个24 bit移位寄存器,用来产生串行输出,根据声道时钟(LRCK)的动作判断读取并行输入。并/串转换流程如图7所示。

图7 并/串转换流程图。

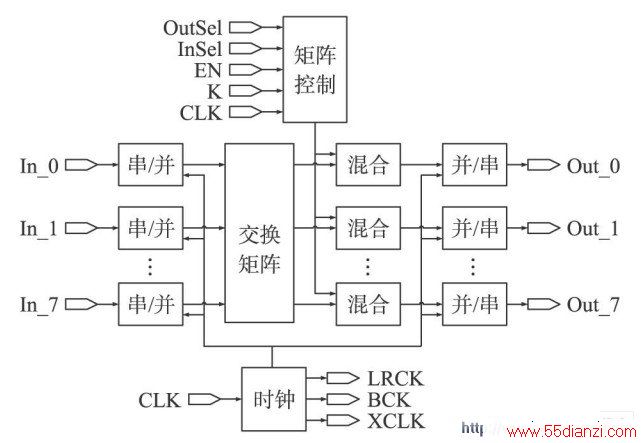

3 系统仿真及实现

3. 1 系统仿真

FPGA总体端口及模块框图如图8所示。

图8 FPGA总体端口及模块框图。

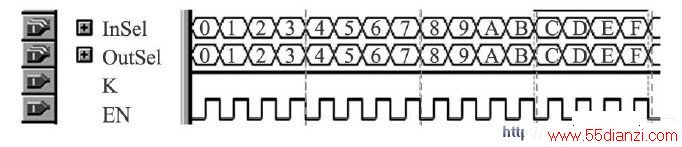

由时钟输入端(CLK)输入50 MHz时钟信号;在交换控制端口送入控制信号,使In_0与Out_0相连, In_1与Out_1相连, ……, In_7与Out_7相连,控制信号输入如图9所示。

图9 控制信号输入。

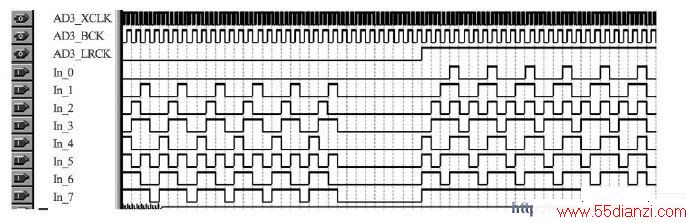

在第一路串行信号输入端( In_0)的左声道输入时序输入16进制串行数据000000,在右声道输入时序输入111111;同理,在In_1的左声道输入时序输入222222,在右声道输入时序输入333333; ?在In_7的左声道输入时序输入EEEEEE,在右声道输入时序输入FFFFFF。串行数据输入如图10所示。

图10 串行数据输入。

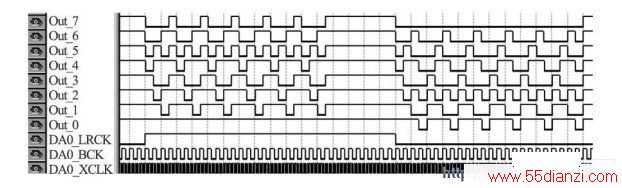

系统的串行输出端有相应数据输出, Out_0 端左声道输出数据为000000, 右声道输出数据为111111,与In_0输入数据一致;Out_1端左声道输出数据222222,右声道输出数据333333,与In_1输入数据一致; ?; Out_7 端左声道输出数据EEEEEE,右声道输出数据FFFFFF,与In _7 输入数据一致。

串行数据输出如图11所示。

图11 串行数据输出。

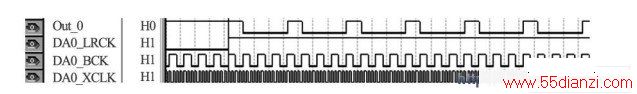

改变控制端口数据,使In_1的左声道输入(数据为222222 ) 与In _ 2 的右声道输入(数据为555555)与Out_0的左声道输出连接。由图3 - 5可见,Out_0串行数据输出变为777777。串行数据混合输出如图12所示。

由以上仿真结果可知, FPGA 整体设计能够实现串行数字音频信号的交换与混合,达到预期设计要求。

图12 串行数据混合输出。

3. 2 系统实现

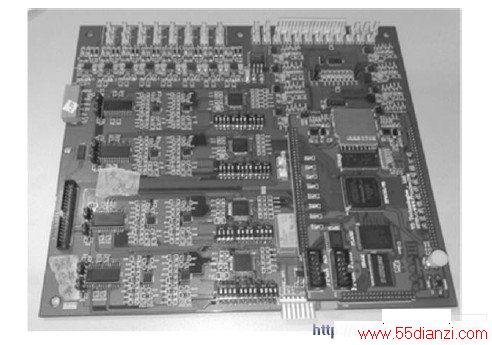

交换混合矩阵实物照片如图13所示。

图13 交换混合矩阵实物照片

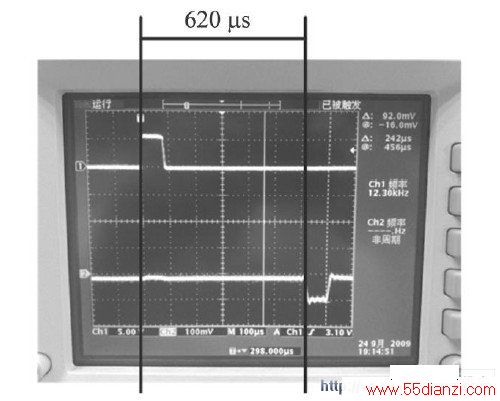

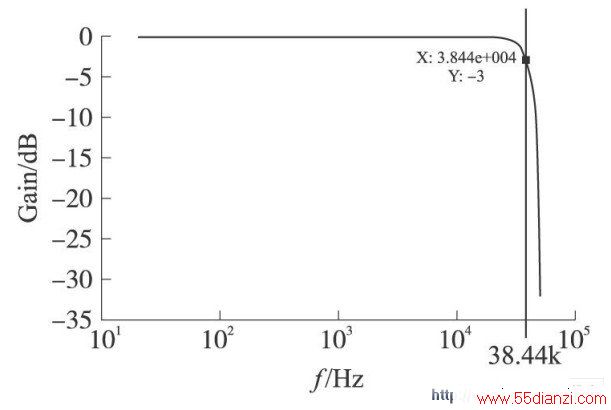

实物测试时,先将交换混合矩阵接入嵌入式控制系统,利用嵌入式控制系统对其进行控制。采用计算机、MP3、便携式CD 机、 信号发生器 等播放的音频信号作为输入源, 扬声器 及耳机、 示波器 等作为输出设备,测试交换、混合及音量调节功能。经*测试,输出音频信号无明显失真。在多路音频信号混合输出时,仍然可以保证较好的信号质量。输入输出延时的测量波形如图14所示,约为620μs。通过逐点测量得到幅频特性曲线如图15所示,通频带为20 Hz~38. 44 kHz。

图14 输入输出延迟测量波形。

图15 幅频特性曲线。

测试结果证明,交换混合矩阵能够正确接受控制系统的命令,完成音频信号的交换、混合及音量调节功能。

4 结论

本文针对音频交换系统应用需求,提出了一种基于FPGA音频交换混合矩阵的设计方案,并进行软硬件设计阐述及仿真,并完成了实物制作与测试。

本文所述方案采用FPGA作为交换混合矩阵的核心器件,因此具有较强的通用性,可根据实际需要裁减或增加交换容量、配置音频信号采样频率及采样精度等特点。

经仿真及实物测试,基于FPGA的音频交换混合矩阵能够实现音频信号的交换、混合及音量调节,同时具有延时低、隔离度高、音质好的特点,可适用于各种会议、指挥、通信等场合。

本文关键字:暂无联系方式EDA/PLD技术,单片机-工控设备 - EDA/PLD技术