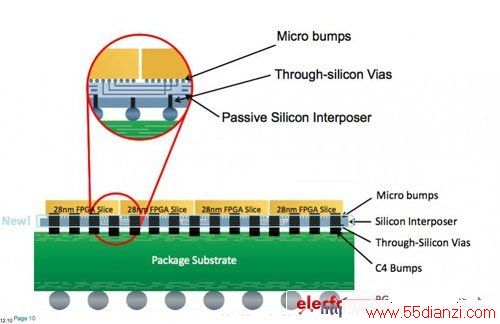

赛灵思的FPGA 3D堆叠技术

最后,赛灵思则在去年宣布推出可将多块FPGA核心通过3D堆叠技术集成在单片封装中的技术,并将把这种技术应用在其28nm制程7系列FPGA产品上。有关的产品定于今年下半年上市。

另:

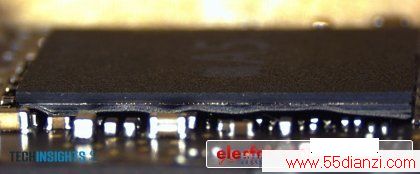

A5芯片侧面肉眼可见上下层芯片的分界结构

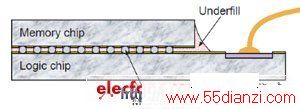

苹果A4/A5处理器虽然也使用了类似3D芯片堆叠的技术,但并没有使用TSV和Interposer结构,而是采用如上图所示的结构,直接通过Microbump实现内存芯片与逻辑芯片的互联。

本文关键字:技术 EDA/PLD技术,单片机-工控设备 - EDA/PLD技术