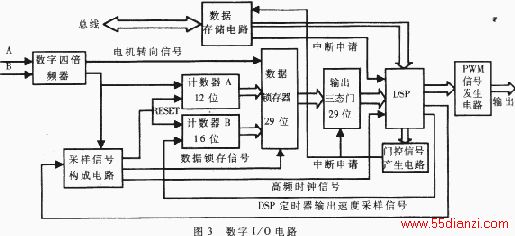

该电路包括采样信号构成电路、数字四倍频电路、12位测速脉冲计数器A、16位高频时钟脉冲计数器B、数据锁存器(29位)、输出三态门(29位)。其电路结构如图3所示。因为ISP器件的I/O单元作为输出时具有三态缓冲特性,故利用其中的29个I/O单元构成输出三态门,连到DSP的32位数据总线上。该输出三态门的门控信号由门控信号产生电路将DSP的READ信号、IOSTRB信号及片选信号组合而成,该信号接到29个输出三态门的输出使能端上,供DSP读取。中断响应时只需要一次读就可将电机转向信号、四倍频测速脉冲计数值、高频时钟脉冲计数值读入DSP中。数字四倍频电路将光电编码器发出的正交编码脉冲(A相、B相)细分后产生四倍频脉冲供计数、采样使用。同时,正交编码脉冲还将产生电机转动方向信号。采样信号构成电路将DSP发出的速度采样脉冲及数字四倍频电路输出的脉冲综合后,按数据锁存、中断申请、计数器清零的顺序发出脉冲信号,控制采样逻辑的顺序。测速脉冲计数器、高频时钟脉冲计数器是根据电机每转输出的脉冲数及最高转速设计的12位及16位不可逆计数器。

2.2 转速给定数据存储电路

该电路包括16位数据锁存器、输出三态门(16位)、中断信号产生电路。其作用是将上位机发出的转速给定数字信号锁存在数据锁存器中,并向DSP发出中断请求信号。当DSP响应中断时,通过门控信号产生电路发出门控信号,控制16个输出三态门的输出使能端,将数据锁存器中转速给定数字信号读到DSP中,作为速度环的给定信号。

2.3 PWM信号产生电路

该电路包括6位PWM数据锁存器、PWM时序电路、锁存延时器。DSP定时发出写数据信号,其数据总线中的一位与地址译码器译码信号在锁存延时器中组合,延时器的输出锁存信号确保数据总线上的数据被正确地锁存至PWM数据锁存器中。其输出经过PWM时序电路的调节与时序校正,产生PWM信号。PWM时序电路同时保证PWM信号以先关断、后开通的方式控制智能功率器件,避免相同桥路上的功率器件同时导通而发生短路事故。

全数字I/O电路设计完成后,首先利用软件仿真器进行了软件仿真调试工作,在软件调试的基础上还进行了硬件调试。硬件调试完成后,将ISP器件作为脉冲信号发生器以产生其它器件所需的脉冲调试信号,进行电路板的硬件调试,从而加快整个硬件系统的调试工作。所设计的单片全数字I/O电路已用于全数字交流位置伺服控制系统中,运行结果表明位置伺服精度达到设计目标。

本文关键字:暂无联系方式电工文摘,电工技术 - 电工文摘