全桥变换器的RD缓冲电路

点击数:7506 次 录入时间:03-04 11:37:22 整理:http://www.55dianzi.com 电工文摘

图10 基准电压的电源抑制

5 测试

对所设计的ADC芯片进行了流片,图11为用于测试的芯片及其接口,其中间部分就是所设计的芯片。

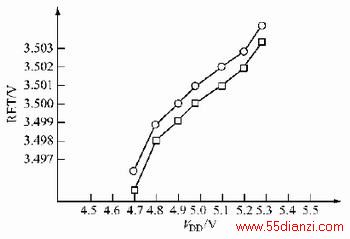

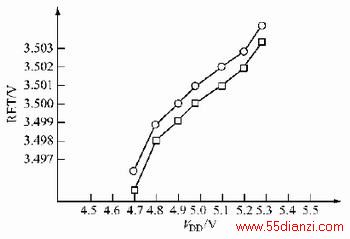

对芯片进行了测试:改变工作电压,对基准电压的输出端RET进行测试,其结果如图12所示,结果表明:在工作电压范围内,基准电压源的最大偏差为5mV。同样测得REB的值,计算同一V

DD时RET-REB的值,可得其值恒定为2.0V,因此所设计的片上基准电压源的电源抑制比高,而且RET-REB的差值恒定,为ADC中的比较器提供了稳定的比较电压,能很好地满足10位40MSPS的要求。

图11 所设计芯处片及接口

图12 RET随V

DD变化的测试结果

6 结论

由于采用了新型的高增益CMOS运算放大器作为带隙基准电压源的运算放大器,从而大大提高了带隙电压源的精度,并且采用基准电压的差值作为ADC中比较器的比较电压,更进一步减小了误差,经测试所设计的基准电压源能很好满足ADC的要求。所设计的基准电压源具有面积小、低温度系数以及随电源电压变化的偏差小等特点。

上一页 [1] [2]

本文关键字:暂无联系方式电工文摘,电工技术 - 电工文摘