摘要:在消费类产品小型化和更轻、更薄发展趋势的推动下,厂商开发了更小的封装类型。实际上,封装已经成为新设计中选择还是放弃某一器件的关键因素。本文首先定义了“倒装芯片”和“晶片级封装”两个名词,介绍晶片级封装(WLP)技术的开发。然后,讨论使用晶片级封装器件的实际情况。讨论主题包括:如何确定某一器件能否使用倒装芯片/UCSP™封装;通过标识识别倒装芯片/UCSP;晶片级封装的可靠性;查找适用的可靠性信息。在本文总结部分,展望了今后的封装技术发展,列出本应用笔记的参考文献以及本文没有讨论的某些主题和相关资料链接等。

引言

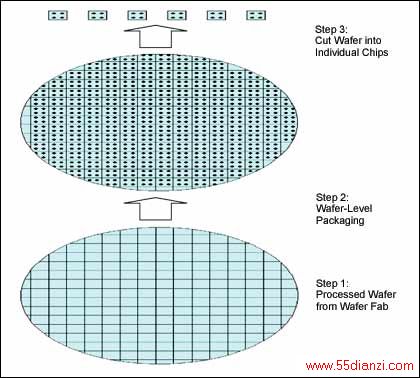

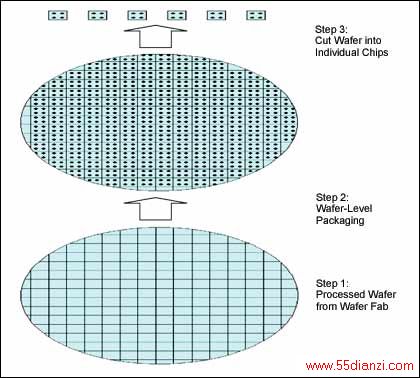

半导体技术的进步大大提高了芯片中的晶体管数量和功能,这一集成规模在几年前还无法想象。现在我们认识到,如果没有IC封装技术同样令人振奋的发展,也不可能实现便携式电子产品的设计。在消费类产品小型化和更轻、更薄发展趋势的推动下,厂商开发了更小的封装类型。最小的封装当然是芯片本身,图1描述了IC从晶片到单个芯片的实现过程,图2是一个实际的晶片级封装(CSP)。

晶片级封装的概念起源于1990年,在1998年定义的CSP分类中,晶片级CSP是多种应用的一种低成本选择,这些应用包括EEPROM等引脚数量较少的器件,以及ASIC和微处理器等。CSP采用称为晶片级封装(WLP)的工艺进行加工,WLP的主要优点是所有装配和测试都在晶片上进行。随着晶片尺寸的增大、管芯的缩小,WLP的成本不断降低。作为最早采用该技术的公司, Dallas Semiconductor在1999年便开始销售晶片级封装产品。

图1. 晶片级封装(简图)最终将每个芯片从处理过的晶片上分离出来。

图2. 12焊球晶片级封装,3 x 4焊球,2个空焊球位置

命名规则

业界在WLP的命名上还有分歧。CSP晶片级技术非常独特,封装内部并没有采用键合方式。封装芯片的命名也有分歧。常用名称有:倒装芯片(STMicroelectronics和Dallas Semiconductor®)、CSP、晶片级封装、WLCSP、WL-CSP、MicroSMD (National Semiconductor)、UCSP (Maxim Integrated Products)、凸起管芯以及MicroCSP (Analog Devices)等。

对于Maxim®/Dallas Semiconductor,“倒装芯片”和“晶片级封装”最初是所有晶片级封装的同义词。过去几年中,封装有了进一步的细分。在本文档以及所有Maxim资料中,包括公司网站,“倒装芯片”是指焊球具有任意形状、可放在任何位置的晶片级封装管芯(边沿有空隙)。 “晶片级封装”是指在间隔规定好的栅格上有焊球的晶片级封装管芯。图3解释了这些不同,注意,并不是所有栅格位置都要有焊球。

图3中的倒装芯片尺寸反映了第一代Dallas Semiconductor的WLP产品;晶片级封装尺寸来自各个供应商,包括Maxim。目前,Maxim和Dallas Semiconductor推出的新型晶片级封装产品的关键尺寸列在表1中。

图3. 图中显示了晶片级封装和倒装芯片封装的典型尺寸以及区别。

表1. Maxim和Dallas Semiconductor UCSP (晶片级封装)的标称尺寸7 ParameterDesignatorValueNo. of Bumps(---)4 to 36Bump Diameterb0.30, 0.35mmBump HeightA10.25, 0.3mmBump Pitche0.5mmDie ThicknessA20.33, 0.38mm

晶片级封装(WLP)技术

提供WLP器件的供应商要么有自己的WLP生产线,要么外包封装工艺。各种各样的生产工艺必须能够满足用户的要求,以确保最终产品的可靠性。Wafer-Level Packaging Has Arrived 8、The Wafer-Level Packaging Evolution9、WLCSP Technology Direction 10等文章生动地介绍了WLP的过去和未来。美国亚利桑那州凤凰城的FCI、美国北卡罗莱纳州的Unitive®建立了WLP技术标准,产品名为UltraCSP (FCI)和Xtreme (Unitive)。Amkor在并购了Unitive后,为全世界半导体行业提供WLP服务11。

在电路/配线板上将芯片和走线连接在一起的焊球最初采用了锡铅共晶*合金(Sn63Pb37)。为了减少电子产品中的有害物质(RoHS),半导体行业不得不采用替代材料,例如无铅焊球(Sn96.5Ag3Cu0.5)或者高铅焊球(Pb95Sn5)。每种合金都有自己的熔点,因此,在元件组装回流焊工艺中,温度曲线比较特殊 (在特定温度上保持一段时间)。

集成电路的目的在于提供系统需要的全部电子功能,并能够装配到特定封装中。芯片上的键合焊盘通过线键合连接至普通封装的引脚上。普通封装的设计规则要求键合焊盘位于芯片周界上。为避免同一芯片出现两种设计(一种是普通封装,一种是CSP),需要重新分配层来连接焊球和键合焊盘。

确定倒装芯片/UCSP的可行性,符合无铅要求

Maxim/Dallas Semiconductor只有一小部分器件采用了倒装芯片或UCSP。识别封装最简单的方法是利用公司网站上的器件快速浏览网页。进行型号搜索后,会显示数据资料的快速浏览页,它包括器件的简要说明、关键特性、封装选择以及应用笔记的URL和详细信息的链接(例如,可靠性报告、评估套件)等。在快速浏览页的右上角可以找到型号的数据资料,如果多个型号使用同一份数据资料,型号表上有下拉框选择特定的型号。点击Go,打开一个窗口,显示定购型号、封装说明、封装外形的URL、温度范围以及封装是否无铅等。查找FCHIP或UCSP,Dallas Semiconductor器件的倒装芯片/UCSP标识符是“X”。Maxim UCSP一般使用后缀“B”,随后是型号的数字部分12。型号表中的封装外形总是含有定位标识,由于UCSP外形用于管芯大小不同的多种器件,因此,没有包括焊球的电配置参数,这些信息在器件的数据资料中提供。而倒装芯片外形只用于特定芯片,因此,其外形一般包括电配置参数。

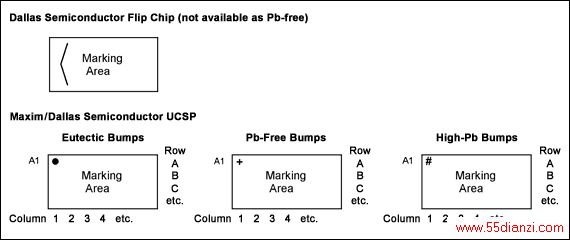

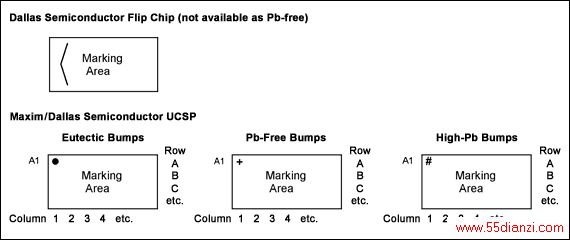

倒装芯片/UCSP顶标(器件标识)

与塑料封装常用的方式不同,大部分倒装芯片和UCSP没有给标准标识方式留有足够的空间。最小的UCSP (4个焊球)只有足够的定位标识和两行6字符代码的空间。定位标识还表明封装是“标准”(共晶焊球)、高铅(#)还是无铅(+),见图4。

图4. 倒装芯片和UCSP标识模板

可以在快速浏览页的更多信息部分了解UCSP的顶标代码。某些情况下,数据资料中也有这些信息。对于反向查找,例如,从顶标确定器件的封装,可以使用网站上的顶标代码功能或下载完整的顶标表13,利用搜索功能识别相应器件。顶标代码用于包含12个焊球的UCSP。更大的UCSP有足够的空间打上全部型号以及日期代码等详细信息。表2所示为Maxim器件使用的商标。

表2. 典型的Maxim UCSP商标

Maxim BrandLegend2-lines mmm nxxmmm Topmark codepppp Part number (numeric portion only)sss Part number suffixn Production-related code, numberxx Production-related code, lettersYWW Date codeIf branded, "MAX" is in the same line as the A1 marker.3-lines mmm nxx YWW4-lines pppp sss nxx YWW4-lines,

alternate pppp sss n YWW xxxxx5-lines MAX pppp sss n YWW xxxxx

表3中的商标类型也适用于Dallas Semiconductor的倒装芯片和UCSP。激光标识非常小,需要放大镜才能看清楚。Dallas Semiconductor的倒装芯片对最小器件采用类似方法,2位器件代码(也称为系列码)之后是管芯的版本号,这一方法不需要交叉参考列表。

表3. 典型的Dallas Semiconductor的倒装芯片和UCSP商标

Dallas Semiconductor BrandLegend1-line dcrr

dc 2-digit device (family) codepppp Part number (numeric portion only)YYWW Date code

Alternate date coderr Die revision code###xx Production-related code2-lines DSpppp rr

[1] [2] 下一页

本文关键字:技术 电力配电知识,电工技术 - 电力配电知识

dc 2-digit device (family) codepppp Part number (numeric portion only)YYWW Date code

dc 2-digit device (family) codepppp Part number (numeric portion only)YYWW Date code Alternate date coderr Die revision code###xx Production-related code2-lines DSpppp rr

Alternate date coderr Die revision code###xx Production-related code2-lines DSpppp rr