为使此电路具有16位D/A转换器的性能,采用第三个数字电位器(U2a)跨接在两个运放(U4a和U4b)的输出端之间。U3a和U3b的编程设定经数字电位器后的电压值。如果VDD为5V,可以将U3a和U3b的输出编程为相差19.61mV。此电压大小经第三个8位数字电位器R3,则自左至右整个电路的LSB大小为76.3mV。此电路获得最优性能所需的严格器件规格如表1所示。

此电路有两种基本工作模式。第一种模式可用于获得可编程、可调节的直流差分电压。在此模式中,电路的数字部分只是偶尔使用,在正常工作时不使用。第二种模式是可以将此电路用作任意波形发生器。在此模式中,电路的数字部分是电路运行的必需部分。此模式中可能发生电容耦合的危险。

图2所示电路的第一次布线如图3所示。此电路是在实验室中快速设计出的,没有注意细节。在检查布线时,发现将数字走线布在了高阻抗模拟线路的旁边。需要强调的是,第一次就应该正确布线,本文的目的是为了讲解如何识别问题及如何对布线做重大改进。

看一下此布线中不同的走线,可以明显看到哪里可能存在问题。图中的模拟走线从U3a的抽头连接到U4a放大器的高阻抗输入端。图中的数字走线传送对数字电位器设置进行编程的数字码。

在测试板上经过测量,发现数字走线中的数字信号耦合到了敏感的模拟走线中,参见图4。

系统中对数字电位器编程的数字信号沿着走线逐渐传输到输出直流电压的模拟线路。此噪声通过电路的模拟部分一直传播到第三个数字电位器(U5a)。第三个数字电位器在两个输出状态之间翻转。解决这个问题的方法主要是分隔开走线,图5示出了改进的布线方案。

改变布线的结果如图6所示。将模拟和数字走线仔细分开后,电路成为非常“干净”的16位D/A转换器。图中的波形是第三个数字电位器的单码转换结果76.29mV。

结语

数字和模拟范围确定后,谨慎布线对获得成功的PCB是至关重要的。尤其是有源数字走线靠近高阻抗模拟走线时,会引起严重的耦合噪声,这只能通过增加走线之间的距离来避免。

AD转换器的精度和分辨率增加时使用的布线技巧。

最初,模数(A/D)转换器起源于模拟范例,其中物理硅的大部分是模拟。随着新的设计拓扑学发展,此范例演变为,在低速A/D转换器中数字占主要部分。尽管A/D转换器片内由模拟占主导转变为由数字占主导,PCB的布线准则却没有改变。当布线设计人员设计混合信号电路时,为实现有效布线,仍需要关键的布线知识。本文将以逐次逼近型A/D转换器和∑-△型A/D转换器为例,探讨A/D转换器所需的PCB布线策略。

逐次逼近型A/D转换器的布线

逐次逼近型A/D转换器有8位、10位、12位、16位以及18位分辨率。最初,这些转换器的工艺和结构是带R-2R梯形电阻网络的双极型。但是最近,采用电容电荷分布拓扑将这些器件移植到了CMOS工艺。显然,这种移植并没有改变这些转换器的系统布线策略。除较高分辨率的器件外,基本的布线方法是一致的。对于这些器件,需要特别注意防止来自转换器串行或并行输出接口的数字反馈。

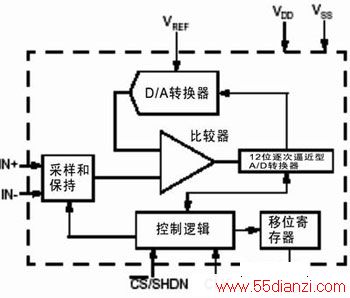

从电路和片内专用于不同领域的资源来看,模拟在逐次逼近型A/D转换器中占主导地位。图1是一个12位CMOS逐次逼近型A/D转换器的方框图。

此转换器使用了由电容阵列形成的电荷分布。

在此方框图中,采样/保持、比较器、数模转换器(DAC)的大部分以及12位逐次逼近型A/D转换器都是模拟的。电路的其余部分是数字的。因此,此转换器所需的大部分能量和电流都用于内部模拟电路。此器件需要很小的数字电流,只有D/A转换器和数字接口会发生少量开关。

这些类型的转换器可以有多个地和电源连接引脚。引脚名经常会引起误解,因为可用引脚标号区分模拟和数字连接。这些标号并非意在描述到PCB的系统连接,而是确定数字和模拟电流如何流出芯片。知道了此信息,并了解了片内消耗的主要资源是模拟的,就会明白在相同平面(如模拟平面)上连接电源和地引脚的意义。

例如,10位和12位转换器典型样片的引脚配置如图2所示。

图2. 逐次逼近型A/D转换器,无论其分辨率是多少位,通常至少有两个地连接端:AGND和DGND。此处以Microchip的A/D转换器 MCP4008和MCP3001为例。

对于这些器件,通常从芯片引出两个地引脚:AGND和DGND。电源有一个引出引脚。当使用这些芯片实现PCB布线时,AGND和DGND应该连接到模拟地平面。模拟和数字电源引脚也应该连接到模拟电源平面或至少连接到模拟电源轨,并且要尽可能靠近每个电源引脚连接适当的旁路电容。象MCP3201这样的器件,只有一个接地引脚和一个正电源引脚,其唯一的原因是由于封装引脚数的限制。然而,隔离开地可增大转换器具有良好和可重复精度的可能性。

对于所有这些转换器,电源策略应该是将所有的地、正电源和负电源引脚连接到模拟平面。而且,与输入信号有关的‘COM’引脚或‘IN’引脚应该尽量靠近信号地连接。

对于更高分辨率的逐次逼近型A/D转换器(16位和18位转换器),在将数字噪声与“安静”的模拟转换器和电源平面隔离开时,需要另外稍加注意。当这些器件与单片机接口时,应该使用外部的数字缓冲器,以获得无噪声运行。尽管这些类型的逐次逼近型A/D转换器通常在数字输出侧有内部双缓冲器,还是要使用外部缓冲器,以进一步将转换器中的模拟电路与数字总线噪声隔离开。

这种系统的正确电源策略如图3所示。

图3.对于高分辨率的逐次逼近型A/D转换器,转换器的电源和地应该连接到模拟平面。然后,A/D转换器的数字输出应使用外部的三态输出缓冲器缓冲。这些缓冲器除了具有高驱动能力外,还具有隔离模拟和数字侧的作用。

高精度∑-△型A/D转换器的布线策略

高精度∑-△型A/D转换器硅面积的主要部分是数字。早期生产这种转换器的时候,范例中的这种转变促使用户使用PCB平面将数字噪声和模拟噪声隔离开。与逐次逼近型A/D转换器一样,这些类型A/D转换器可能有多个模拟地、数字地和电源引脚。数字或模拟设计工程师一般都倾向于将这些引脚分开,分别连接到不同的平面。但是,这种倾向是错误的,尤其是当您试图解决16位到24位精度器件的严重噪声问题时。

对于有10Hz数据速率的高分辨率∑-△型A/D转换器,加在转换器上的时钟(内部或外部时钟)可能为10MHz或20MHz。此高频率时钟用于开关调制器和运行过采样引擎。对于这些电路,与逐次逼近型A/D转换器一样,AGND和DGND引脚也是在同一地平面上连接在一起。而且,模拟和数字电源引脚也最好在同一平面上连接在一起。对模拟和数字电源平面的要求与高分辨率逐次逼近型A/D转换器相同。

必须要有地平面,这意味着至少需要双面板。在此双面板上,地平面至少要覆盖整个板面积的75%。地平面层的用途是为了降低接地阻抗和感抗,并提供对电磁干扰(EMI)和射频干扰(RFI)的屏蔽作用。如果在电路板的地平面侧需要有内部连接走线,那么走线要尽可能短并与地电流回路垂直。

结论

对于低精度的A/D转换器,如六位、八位或甚至可能十位的A/D转换器,模拟和数字引脚不分开是可以的。但当您选择的转换器精度和分辨率增加时,布线要求也更严格了。高分辨率逐次逼近型A/D转换器和∑-△型A/D转换器,都需要直接连接到低噪声模拟地和电源平面。

要解决信号完整性问题,最好有多个工具分析系统性能。如果在信号路径中有一个A/D转换器,那么当评估电路性能时,很容易发现三个基本问题:所有这三种方法都评估转换过程,以及转换过程与布线及电路其它部分的交互作用。三个关注的方面涉及到频域分析、时域分析和直流分析技术的使用。本文将探讨如何使用这些工具来确定与电路布线有关问题的根源。我们将研究如何决定找什么;到哪里找;如何通过测试检验问题;以及如何解决发现的问题等。

本文关键字:暂无联系方式布线-制版技术,电子学习 - 布线-制版技术

上一篇:教你如何看懂印刷电路板