为了补偿谐振电路匹配的额外衰减,截止频率应为所需通带高端的125%.例如,如果需要一个20 MHz带宽、中心频率为140 MHz的滤波器,截止频率应设为(140 MHz + 20 MHz ÷ 2)× 125% = 188 MHz.

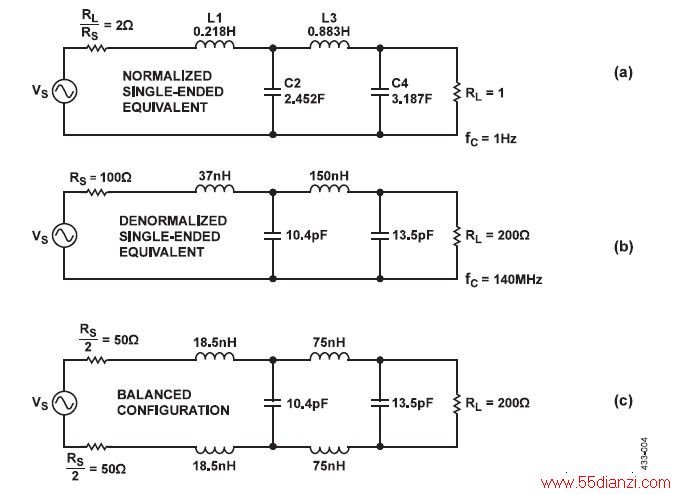

图4(a)显示单端四阶单位标准归一化原型滤波器的一个示例。所示巴特沃兹滤波器在2:1负载-源阻抗比下提供平坦响应,无纹波。

第3步-按频率和负载比例调整标准归一化原型值。

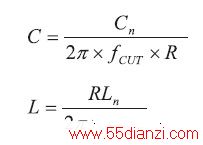

现在可以将单端单位标准归一化原型滤波器值Cn或Ln按比例调整到所需截止频率fcut和负载阻抗R.变换公式如下:

图4(b)显示的是截止频率为188 MHz、负载阻抗为200Ω的单端等效网络。

第4步-通过分割串联电抗将单端等效网络转换为差分网络。

具有高动态范围IF采样功能的多数高速ADC都采用差分输入接口。因此,有必要将单端网络转换为差分网络,如图4 (c)所示。转换为差分网络时,串联阻抗值减半。

图4. 原型滤波器设计步骤。

第5步-消除ADC输入端的原始开关电容。

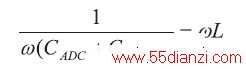

在谐振匹配或储能电路中的分流电感有助于消除片内ADC输入电容(以及在低通滤波器最后一级外增加的任何额外电容)。电感值必须以谐振方式抵消虚部导纳,仅剩下复合阻抗的导电部分。

例如,AD9640差分输入阻抗在140 MHz下为4.7kΩ,与3.9pF并联。

因此所需电感L为331 nH.

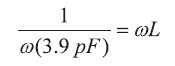

注意,L/C比是决定Q和选择性的因素之一。对于并联谐振电路而言,电感越高,电容越低,通带滤波器带宽越大。为了获得更大的窄带响应,可通过并联添加额外电容来获得更高Q值(除低通巴特沃兹滤波器的最后电容级外)。在下列公式中,添加了一个额外10 pF,将所需电感L降低至93 nH:

因此,Q值越低,响应带宽也就越低。

第6步-装配。

计算好每个接口元件后,可将电路装配在一起进行仿真。通常情况下,为获得滤波器要求的最佳组合,需要借助一些仿真试验和误差来优化网络接口。利用可准确体现实际L值和C值寄生效应的真实元件模型(s参数)来模拟网络响应是有利的。

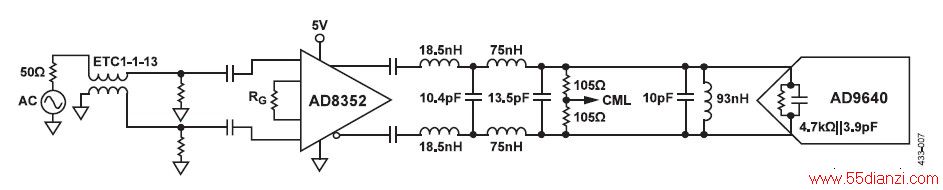

采用理想L值和C值的实施方案如图7所示。注意,考虑电路板走线的寄生串联感应,最终实施可以选用电感值稍低的电感。还需要注意的是,图4(c)中的负载被图7中的ADC接口取代,包括一个并联电感和多个共模偏置电阻。偏置电阻给各差分输入端提供所需的直流偏置,并与ADC输入阻抗和谐振并联电感为滤波器组成一个精确负载。

图7. AD8352和AD9640的ADC接口示例,理想元件

第7步-电路板级经验调谐。

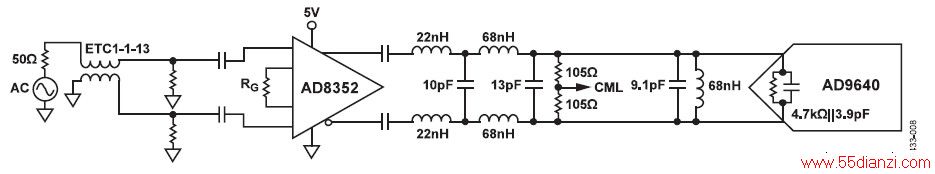

采用的实际L值和C值的最终实施方案如图8 所示。在使用最终仿真值填充电路板后,可能需要一些板级经验优化方法来帮助补偿实际PCB寄生效应。

图8. AD8352和AD9640的ADC接口示例,实际元件

为此,建议使用优良软件和s参数在工艺早期进行详细的仿真。这样,可以减轻更耗时的板级调谐工作。在一些实例中,可能需要为印刷电路板寄生电容建模以选择最佳的L值和C值。

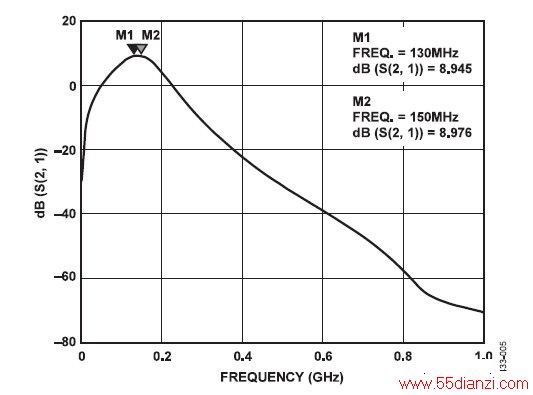

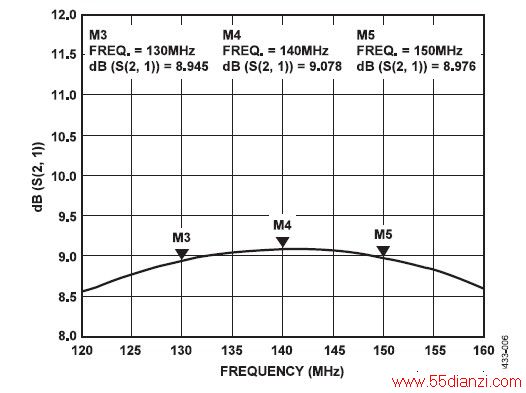

图5和6显示AD8352和AD9640间接口的性能。

图 5. AD8352和AD9640接口示例的滤波器响应

图 6. AD8352和AD9640接口示例的通带平坦度

布局布线考虑

如果滤波器元件值较小,额外的寄生电容会导致大比例的变化,此时降低电路板杂散寄生电容非常重要。为了使本文所讨论的电路达到理想的性能,必须采用出色的布局、接地和去耦技术。至少应采用四层PCB:一层为接地层,一层为电源层,另两层为信号层。有关具体电路板建议,请参看各个器件的驱动器放大器和ADC数据手册。

上一篇:SPI接口的电路设计