3.7 音频格式转换模块

音频格式转换模块采用TI公司的SRC4382芯片。它是一款专用于广播数字音频系统的芯片,它集成了带有采样频率转换的数字音频接口发送器(DIT)和接收器(DIR),2个音频串行接口,以及支持数据和时钟内联的分布式逻辑,DIT和DIR兼容AES3,S/PDIF,IEC 60958和EIAJ CP-1201接口标准,采样频率最高支持216 kHz,并且支持通过I2C总线控制芯片的工作状态。

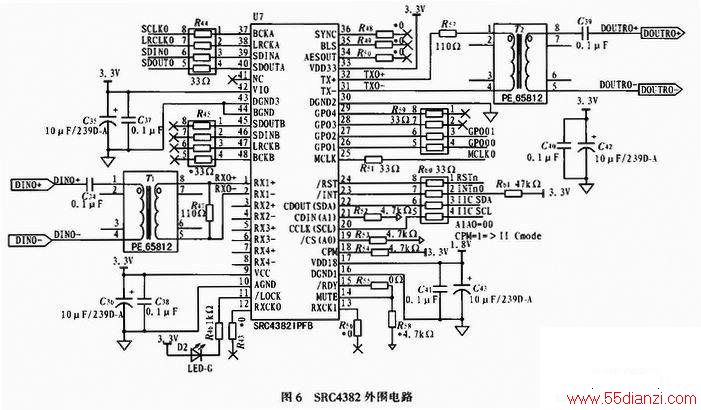

本设计中,通过LPC2138的I2C总线接口控制SRC4382的工作模式,器件地址为0xE0H。通过设置SRC4382内部寄存器,使其同时有2条工作的信号路径,一条为RX+、RX-差分信号经过DIR单元的采样频率转换和解码后,转换为I2S信号,由SDOUT输出;另一条为I2S信号SDIN经过DIT单元的采样频率转换和编码后,转换为数字音频接口AES3信号,由差分线TX+、TX-输出。LRCK与SCLK同CS5368,均由外部提供。RX+、RX-与DIN+、DIN-之间以及TX+、TX-与DOUTR+、DOUTR-之间均需要用变压器做隔离去耦合,以防止前后级之间相互干扰。SRC4382的外围电路如图6所示。

4 软件程序设计

CS5368、CS4382、SRC4382 3款芯片均可通过设置其内部寄存器,获得不同的工作状态。

4.1 CS5368软件部分

系统上电之后需对CS5368进行初始化。GCTL(globalmode control register)控制芯片的工作模式,本设计工作状态为:控制端口模式,时钟为256采样率,输出I2S模式,从模式下的所有采样频率。因此GCTL的值设置为0x87H。其他寄存器保持默认值即可。初始化程序如下:

//I2C写一个字节0x87到地址GCTL(0x01)

I2c_WriteNByte(CS5368_Addr,1,GCTL,&gctl,1);

当CS5368发生溢出中断时,会向LPC2138的外部中断INT0发送中断信号,同时LED灯D1被点亮。在中断程序中,查询OVFL寄存器状态,设置相应通道的输出消声(mute)。中断服务程序如下:

char ovfl,mute;

I2c_ReadNByte(CS5368_Addr,1,OVFL,&ovfl,1);

mute=~ovfl;

I2c_WriteNByte(CS5368_Addr,1,MUTE,&mute,1);

4.2 CS4382软件部分

系统上电之后需对CS4382进行初始化。MC1、MC2和FC共同控制CS4382的工作状态,本设计中将其值分别设置为0x80H,0x10H,0x05H。芯片工作存控制端口模式下,输入音频格式为24位I2S信号,去加重滤波器响应频率为48 kHz。其他寄存器保持默认值。初始化程序如下:

mc1=0x80;mc2=0x10;fc=0x05;

I2c_WriteNByte(Cs4382_Addr,1,MC1,&mc1,1);

I2c_WriteNByte(CS4382_Addr,1,MC2,&mc2,1);

I2c_WritcNByte(CS4382_Addr,1,FC,&fc,1);

4.3 SRC4382软件部分

4.3.1 SRC4382初始化

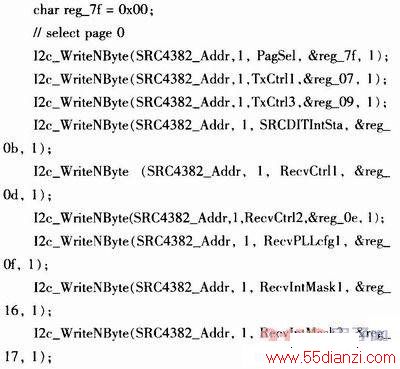

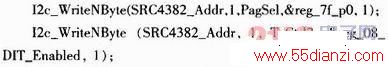

系统上电之后需要对SRC4382进行初始化。SRC4382的寄存器分为4页,第0页为控制和状态寄存器,第1页为DIR通道状态和用户数据缓冲寄存器,第2页为DIT通道状态和用户数据缓冲寄存器,第3页保留。在操作每页寄存器之前,必须通过设置每页的页选择寄存器来确定要操作的页。初始化程序中只需将寄存器07,09,0b,0d,0e,0f,16,17,2d分别设置为0x22,0x02,0x33,0x08,0x09,0x12,0xfe,0x01,0x42,其他保留默认值即可。各寄存器的具体值及其含义请参考技术手册。初始化程序如下:

![]()

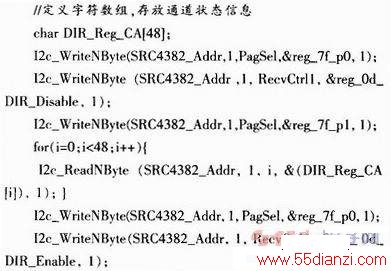

4.3.2 SRC4382读通道状态

由第一部分介绍可知,通道状态中含有丰富的信息。通过读第1页寄存器,便可以获得接收的AES3数字音频的特征信息。读通道状态之前,应先在第0页禁止DIR,然后切换到第1页,读完通道状态后再切换回第0页,使能DIR。读通道状态程序如下:

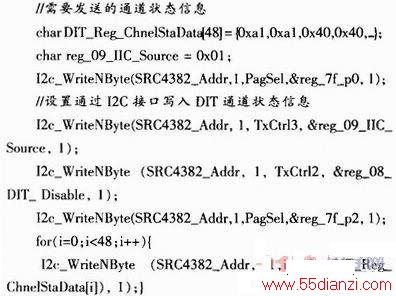

4.3.3 SRC4382写通道状态

通过写第2页的相关寄存器,便可将需要发送的AES3数字音频的特征信息写入到每一帧的通道状态位中。写通道状态之前,应先在第0页禁止DIT,然后切换到第2页,写完通道状态后再切换到第0页,使能DIT。读通道状态程序如下:

5 结束语

该设计通过微控制器LPC2138控制专业音频处理芯片,实现了AES3数字音频接口的设计。本设计中发送的音频信息源和接收处理后的音频信息均可以为模拟信号和串行I2S信号的形式,可用性较强。由于该设计采用专业音频处理芯片实现,因此音质比较好,稳定性比较高。只需简单修改软件部分对音频处理芯片的寄存器配置,即可实现系统特性的改变,所以灵活性和可扩展性较好。该设计可以具体应用于数字调音台的混音器和音频矩阵切换器中,也可以为CD机、MD机的设计提供参考,因此具有较强的工程使用价值。

本文关键字:接口 接口电路,单元电路 - 接口电路