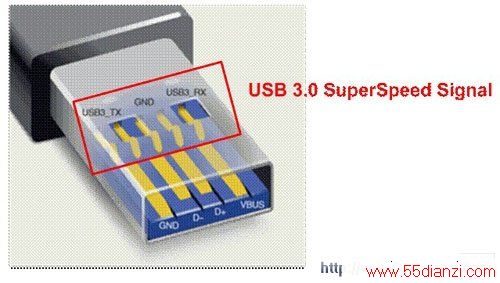

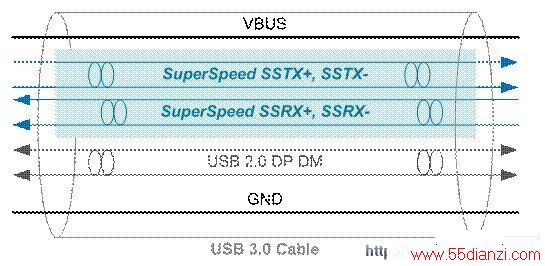

现有的USB 2.0缆线及 连接器 提供了四条 信号线 ,包含VBus 5V 500mA 直流供电,一对DP/DM半双工双向差分信号线,以及GND接地,以此四条接线提供了USB 2.0的480Mbps的资料传输,及直流供电。USB 3.0为了提供高达5Gbps的资料传输率,额外增加五条讯号线,包括两对单向传输的超高速(SuperSpeed)差分讯号: SST X+, S ST X-, SSRX+, SSRX-,及多一组的接地接点,并将直流供电能力提升至5V 900mA。其中的两对差分讯号分别负责传输及接收,提供双向全双工的5Gbps的传输能力。

图1:USB 3.0连接器,后排的USB 3.0 SuperSpeed信号接点

图2:USB 3.0缆线示意图,蓝色部分为SuperSpeed 5Gbps信号

SuperSpeed 5Gbps信号品质的系统设计及量测挑战

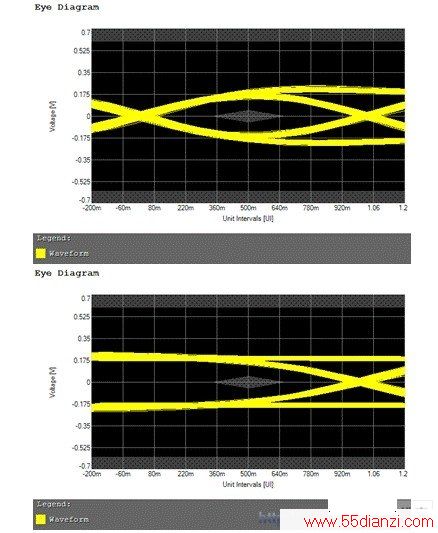

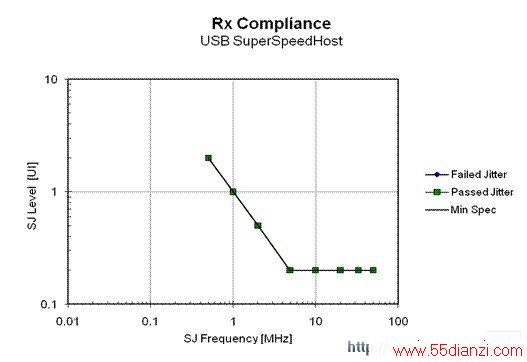

USB 3.0 SuperSpeed位传输率高达5Gbps,且采用开放式 接口 ,信号品质将直接影响装置兼容性及传输效率,与使用者体验息息相关。主控 芯片 、印刷 电路 板、连接器、缆线甚至装置端芯片组,都是影响信号品质的关键。对于芯片厂商的类比传输设计能力,半导体制程变异,系统厂商的印刷电路设计布局都是全新的考验。不同于USB 2.0的经验,信号品质的参考指标将不再只是传输端的眼图(Eye diagram)。USB 3.0独立的传输及接收通道,系统接收能力也成为信号品质及系统设计的重要量测指标。接收端量测主要考验待测物对不同频率的时基误差容忍能力。容忍能力越强的芯片,代表其系统设计可较宽松,可使用较长的信号走线,也有较佳的装置兼容性。

图3: USB 3.0 SuperSpeed传输端信号量测眼图(Eye diagram)

图4: USB 3.0接收量测结果。横轴为时基误差的频率,纵轴为时基误差的振幅。

绿点表示位错误率低于10-12的测试基准点。黑线为测试基准规范。

主机板及笔电的延伸设计

在USB 2.0相当普遍的前端连接口,以内连接的方式连接主机板及主机外箱,提供使用者方便顺手的热插拔应用。USB 3.0连接口势必也将导入前板连接口的设计,额外的连接器及内部 连接线 ,对于信号品质又是外加的考验。

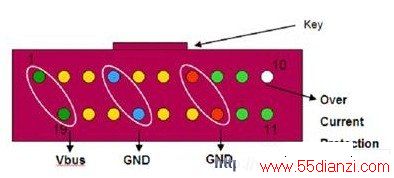

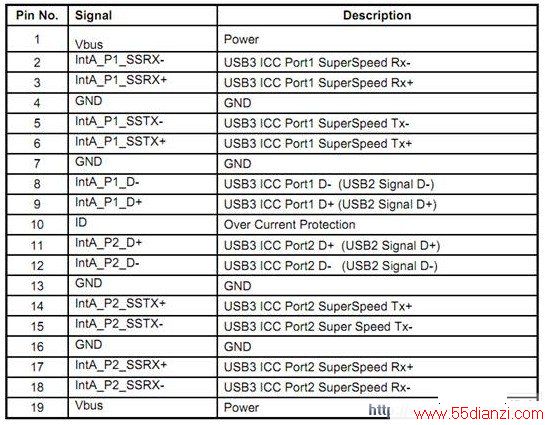

图5: USB 3.0内部连接口针脚定义

此外在笔电设计中,普遍使用软 排线 连接不同的子板,以配合轻薄的外型及机构设计。 软排线 的阻抗控制,软排线连接器的信号连续性,都不如 印刷电路板 及标准 连接头 容易控制。这些都将是未来笔记型 电脑 中USB 3.0连接口的设计挑战。如何在不使用信号 调整器 (re-driver)的额外成本下,导入前板及软排线等系统设计,又维持良好的5Gbps信号品质,成为重要的组件选择关键。

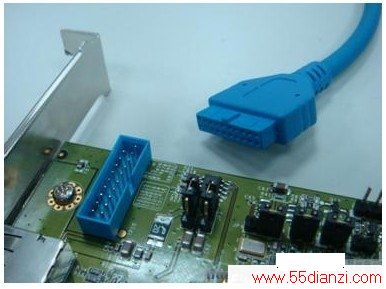

图6: USB 3.0内部连接口及连接线

美商睿思科技的 USB3.0 主端 控制芯片 FL1009,因应前述不同系统设计挑战,整合高效能类比实体设计,完整验证不同系统设计需求。包含可容许长达23公分(9英寸)的线路布局长度,释放系统设计在线路布局(layout)上的局限性,并允许长至45公分的前板USB3.0额外接线,且不需额外re-driver的成本,使系统商与板卡商得以创造最高性能的产品,并有效减少设计时间与成本。除此之外,FL1009也是全球第一颗支持xHCI 1.0的SuperSpeed USB主控端芯片,提供超高效能及绝佳兼容性。

本文关键字:暂无联系方式接口电路,单元电路 - 接口电路

上一篇:硬盘常见故障判断与排除