4.4 偏移错误(OFST)

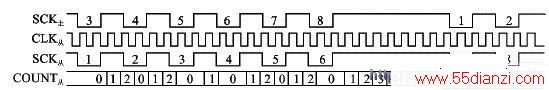

SPI接口一般要求从器件先工作,然后主器件才开始发送数据。有时在主器件往外发送数据的过程中,从器件才开始工作,或者SCK受到外界干扰,从器件未能准确地接收到8个SCK。如图8所示,从器件接收到的8个SCK其实是属于主器件发送相邻的两个数据的SCK主。这时,主器件的SPIF和从器件的SPIF会发生重叠,数据发生了错位,从器件如果不对此进行纠正的话,数据的接收/发送便一直地错下去。

图8偏移错误

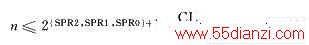

在一个数据的传输过程中,SPR是不允许改变的,即SCK是均匀的,而从图5可以看出,从器件接收到的8个SCK并不均匀,它们是分别属于两个数据的,因此可以计算SCK的占空时间来判断是否发生了偏移错误。经分析,正常时候SCK=1时的时钟周期数n的取值满足如下关系:

但由于主从时钟之间是异步的,并且经过了取整,所以正常时候SCK=1时的时钟周期计数值COUNT应满足:

比如在图5中,COUNT的最大值COUNT(max)=2或者1,都可认为是正常的。但当出现COUNT(max)=8时,可以判定出现了偏移错误。在实际设计中,先记录下第一个COUNT(max)的值,如果后面又出现与记录值相差1以上的COUNT(max)出现,可知有偏移错误OFST发生。SPI接口在“不均匀”的地方令SPIF=1,然后准备等待下一个数据的第一个SCK。其中COUNT的位数固定为8位,为了避免溢出时重新从00H开始计数,当计数达到ffH时停止计数。

4.5 其他错误

设定不当,或者受到外界干扰,数据传输难免会发生错误,或者有时软件对错误的种类判断不清,必须要有一种方法强制SPI接口从错误状态中恢复过来。在SPI不工作,即SPEN=0的时候,清除SPI模块内部几乎所有的状态(专用寄存器除外)。如果软件在接收数据的时候,能够发现数据有错误,无论是什么错误,都可以强制停止SPI的工作,重新进行数据传输。例如,在偏移错误(OFST)中,如果SPR2、SPR1和SPR0的设置适当,也可以使SCK显得比较“均匀”。SPI接口硬件本身不可能检测到有错误,若用户软件能够发现错误,这时就可以强制停止SPI的传输工作,这样就可以避免错误一直持续下去。

在应用中,如果对数据的正确性要求较高,除了要在软件上满足SPI接口的时序要求外,还需要在软件上作适当的处理。

5.设计SPI总线控制器

目前的项目中使用了SPI总线接口的 FLASH 存储器 存储图像数据。FLASH的SPI总线频率高达66M,但MCU的频率较低, 晶振 频率 7.3728M ,SPI最大频率为主频1/2。对于320*240*16的图像读取时间为333ms,而且还忽略了等待SPI传输完成、写显存、地址坐标设定等时间。实际测试约为1s。成为GUI设计的极大瓶颈。由于TFT驱动是自己 FPGA 设计的,资源尚有余量,决定把SPI控制器(主)及写图像部分逻辑放入FPGA中用硬件完成。

首先接触到的是SPI的SCK时钟频率问题。FPGA的频率是48M,未使用 PLL 。能否以此频率作为SCK频率呢?要知道所有的MCU提供的SPI频率最大为主频的1/2!为什么呢?查过一些资料后发现,SPI从机接收数据并不是以SCK为时钟的,而是以主频为时钟对SCK和MISO进行采样,由采样原理得知SCK不能大于1/2主频,也就有了MCU提供最大 master 频率是1/2主频,最大slaver频率是1/4主频。FPGA在只作为主机时能否实现同主频一样频率的SCK呢??答案貌似是肯定的!但我还是有点担心,用组合逻辑控制SCK会不会出现较大毛刺影响系统稳定性呢?

本文关键字:暂无联系方式接口电路,单元电路 - 接口电路