1 系统概述

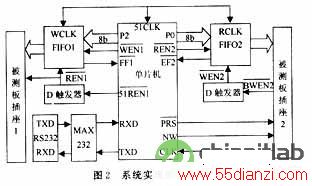

整个系统主要由单片机、FIFO芯片、MAX232芯片以及D触发器芯片构成。图2是系统的原理简图,图中给出 了一些重要的器件和控制信号。

系统的工作流程如下:首先将测试数据从计算机的RS232C口送入单片机,单片机将其变为8 b并行数据写入FIFO1,这期间不对FIFO1进行读操作。FIFO1满后,被测板以40 MHz的总线时钟频率并行读取FIFO1,同时被测板的输出以同样速率写入FIFO2。FIFO2满后,再通过RS232C口将FIFO2中的数据读入PC机,其中的控制操作由单片机及外围电路来完成。下面将分4个步骤介绍系统的工作过程,其中前2个步骤是测试数据从计算机传送到被测板的过程,后面2个步骤描述了被测板的输出结果送回计算机的过程。

1.1 RS232C口与FIFO1的通信(数据从RS232C口输入)

测试数据以串行方式从计算机的RS232C口输出,通过MAX232电平转换后进入单片机的RXD口,再转换为 8 b并行数据从P2口写入到FIFO1。单片机除了控制FIFO1和FIFO2的复位RES(图2中未标出)、FIFO1的写使能WEN1以及FIFO1的写时钟WCLK,还发出一个信号用来辅助读取FIFO1。

由于FIFO1的读取被设置为在数据写入时无效,只有写满了以后才允许被测板读取,因此对于FIFO1满状态的判断及控制非常重要。这里通过计数方式和查询方式同时确定其满状态,方法如下:在单片机内设置一个计数值为256 k的计数器,每送出一个字节,计数器值减1。当计数器减到0,查询FIFO1的管脚的状态,若为低电平,则开启,允许被测板从FIFO1中读出数据,否则向计算机发出错误信号,重新接收数据。

1.2 FIFO1与被测板的通信(数据输入被测板)

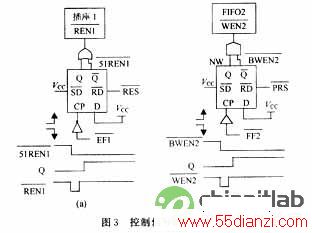

FIFO1与被测板的通信连接包括数据线以及读允许REN1。REN1的的作用是控制被测板的读取过程,只有当此信号为低电平,被测板才能从FIFO1中读数据。

由于被测板的读取速度很高,而单片机的指令周期相对慢得多,当FIFO1被读空后,如果使用单片机来控制读允许使其恢复到高电平,可能在关闭读允许以前被测板已经读入了很多无用数据,所以这里采用FIFO1的空标志位通过D触发器,和单片机的读允许端一起组成控制信号具体电路如图3(a)所示。

当单片机发出读允许信号,被测板开始读取数据,当FIFO1为空,EF1通过D触发器关断使被测板停止读数,同时,单片机关闭FIFO1的读有效信号。

1.3 被测板与FIFO2的通信(数据从被测板输出)

被测板与FIFO2的通信连接包括数据线、写允许、反馈线NW、部分复位PRS以及时钟CLK。PRS 的作用是部分复位FIFO,即将FIFO的读写指针归零,其他设置不变。CLK由被测板提供,作为FIFO1的读时钟和FIFO2的写时钟,这里为40 MHz,当测试不同的单元电路时,CLK的频率也可以随着被测对象的总线频率改变而改变。

被测板对测试信号进行处理后,首先通过PRS将 FIFO2部分复位,防止由于两者没有同时复位带来的数据误读。接着被测板将BWEN2置为低,开始向FIFO2写数据。

当FIFO2被写满,同样存在一个及时关闭其写允许的问题。这里采用FIFO2的满标志位FF2通过D触发器关断同时触发NW信号反馈给被测板,通知被测板停止输出数据,如图3(b)所示。

1.4 FIFO2与RS232口通信(数据从RS232口输出)

FIFO2的满状态除关断其写允许WEN2外,还给单片机一个中断信号,单片机收到此中断后,立即开启读允许REN2(将其置为低电平),开始从FIFO2的空读取数据,FIFO2的空状态判别同样由计数方式和查询方式同时确定,当计数器为0时,测试FIFO2的空状态输出管脚EF2,若结果为低电平,则通知计算机读取过程结束,同时关闭REN2,禁止读出数据,否则通知计算机出错。

至此,一次完整的测试数据处理传输过程已经全部完成。单片机对FIFO进行复位,准备下一次工作。用户可以分析被测板送回的数据,从而测试单元电路的性能。

2 器件选择

本方案中单片机采用AT89C51芯片,包括4个8 b并行I/O口、1个全双工的串行口、2个16 b的定时/计数器以及2个中断源。晶振的工作频率选用11.095 2 MHz,每个机器周期约1μs。单片机在这里主要完成与RS232C口和FIFO通信以及整体流程控制的工作。相对于被测电路的数据速率,单片机的处理速度很低,因此如何用相对低速的器件控制高速信号是本方案要解决的关键问题之一。本文的方法是采用FIFO和TTL芯片来实现数据缓冲和辅助控制。辅助控制器件中的D触发器采用速度较高的74S系列芯片,最高工作频率为110 MHz。

FIFO是一种先进先出 存储 器,允许同时异步进行读写操作,读写之间互相独立。这里选用的FIFO为IDT72V36100芯片,容量为64 k×36 b,工作频率高达133 MHz,是IDT公司SuperSyncⅡ系列高性能同步FIFO中的一种。该系列芯片相比以前的FIFO器件有很多独特的优点。例如具有总线匹配功能(即输入输出数据总线宽度可以不同,有几种匹配方式供用户设置),还有标志位可编程功能以及重发功能,使得设计者能够根据需要设置标志位的地址,并且可以重新读取已经读过的数据。这些 优点大大增加了设计灵活性,给使用者带来很大方便。

本方案中用到FIFO的主要管脚包括写使能WEN1(低有效)、读使能REN1(低有效)、数据输入/输出、总线匹配设置、空标志位(低有效)、满标志位(低有效)以及读写时钟等。IDT72V36100芯片的总线宽度有5种匹配方式,分别为36 b/36 b,36 b/18 b,36 b/9 b,18 b/36 b及9 b/36 b,本方案选用的是36 b/9 b和9 b/36 b的总线匹配方式。实际应用中,根据被测电路的实际情况可以选择不同的总线匹配方式,使用者根据所选的匹配方式将相应的FIFO总线设置管脚置为高电平或低电平。

3 软件流程

系统所用到的软件包括PC机的串口通信程序与单片机程序。PC机的串口通信程序完成的是单纯的通过RS232口与单片机通信的功能,这方面的技术资料很多,因此不再赘述。这里主要介绍的是单片机程序,该程序执行流程控制功能和与PC机通信功能。

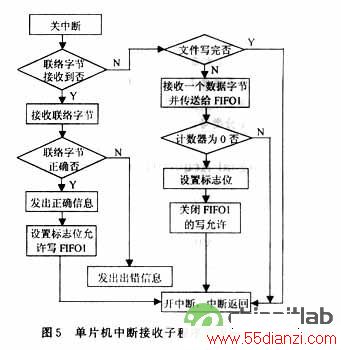

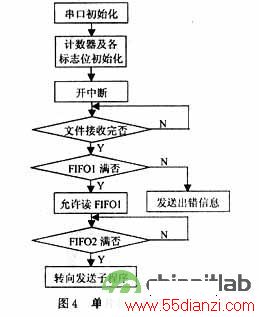

单片机与PC机通信时,接收采用中断方式,发送采用查询方式。图4是单片机主程序流程图。单片机程序中要用到两个标志位,即联络标志位和数据结束标志位,主程序在初始化过程中应该先将这两个标志位清零并设置好计数器。经过初始化以及开中断后,单片机处于等待方式,不断查询数据结束标志位,判断数据是否接收完毕。当查询到标志位被置1后,继续查询FIFO1的满状态管脚,若FIFO1为满,证明数据接收正确,单片机允许读FIFO2,进入等待状态,等待FIFO2变满产生的中断,然后转向发送子程序。

图5是中断接收子程序的流程图。串口每进入一个字节就产生一次串口中断,进入到该子程序中。每次中断都要先检查联络标志位,若该标志位为0,则表明送入的是联络字节,检查该字节和约定的联络信号是否一致,若一致, 表明通信正常,将联络标志位置1;如果联络标志位已被置1,则检查数据结束标志位,若该标志位为0,则将数据以字节为单位写入FIFO1,每次中断写入一个字节,并将计数器减1,若计数器减到零,表明数据传输结束,将数据结束标志位置1并跳出中断。