软件无线电技术及高速模数转换、数字信号处理器件的出现使雷达、通信等信号的采集得以高采样率实现,而智能天线、MIMO等组成的系统都需要多通道实现同步,时钟信号抖动、相噪等特性对AD转换器的性能、阵列信号处理的波束形成等有很大的影响,所以多路同步的高性能时钟信号的设计是高速多通道数据采集系统不可忽视的一部分。

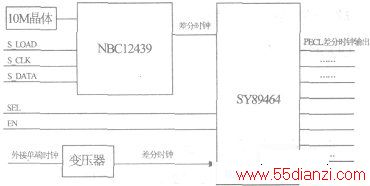

本文通过可编程的锁相环芯片NBC12439和时钟缓冲1:10扇出芯片SY89464给出了一种多通道数据采集卡的时钟设计方案,NBC12439可通过编程实现不同的时钟频率,同时利用SY89464的2:1选择器可以实现板上内部时钟和外接时钟的切换,既方便设计调试,也便于相干系统的数据采集,具有很大的灵活性。电路设计设计通过NBC12439实现内部时钟,采用10M高稳晶振,配置采用串行接口,通过采集板的FPGA实现,NBC12439的时钟输出接SY89464的一路输入,另一路接外输入时钟,10路PECL输出时钟即可接高速AD芯片的时钟信号。NBC12439的/P_LOAD信号接高电平,SY89464的选择输入引脚也连接至FP-GA。电路的连接原理框图如下图,

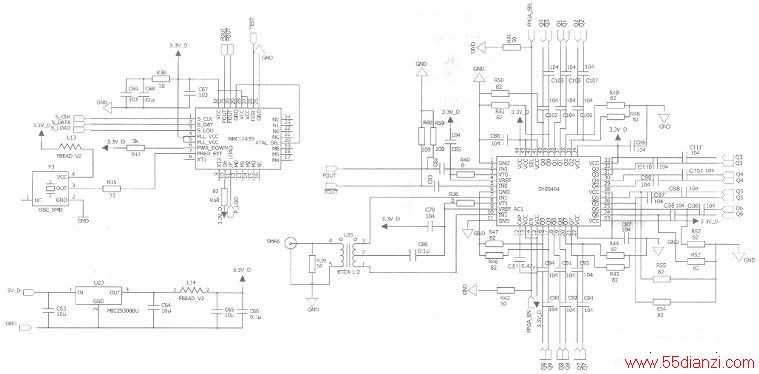

下图为电路图。

NBC12439内的振荡器采用串行谐振电路,最后采用串行谐振模式的晶体,匹配的晶体静电容为5~7pF,若晶体的标称电容大于这个范围,应加一个500Ω~lkΩ的匹配电阻以抑制三次谐波。同时印制板设计中需要注意的是晶体与NBC12439的连线应尽可能短,不应加过孔。同时NBC12439是混合电路,电源设计时应考虑其滤波和去耦,PLL电源和数字部分的电源应分开,滤波设计时应重点去除lkHz-1MHz的噪声,通过RC设计滤波器时,应考虑到电阻上的电压降,因为NBC12429的PLL电源最大吸入电流为28mA,电压降为0.5V,则串连电阻的范围应在10~15Ω内。

SY89464的输出时钟应作等长度限制,空间不够时,可采用蛇行线实现,以消除时滞的影响。

SY89464的POR电容量的设计,取决于电源复位后升至2.3V所需的时间,可由下式计算C(μF)≥TdPs(ms)/12(mS/μF),如所需时间为12ms,则C应不小于1μF。

SY89464的PECL差分输出时钟的阻抗匹配,可采用并行终端匹配或AC耦合匹配,在高速AD的时钟输入,一般采用变压器耦合匹配,通过终端电阻匹配为50Ω。

器件的配置

SY89464的配置只需根据输入到FPGA中的数据控制sel和en引脚电平,以选择时钟输入和使能或取消输出信号,下面主要介绍NBC12439的配置。

NBC12439的输出频率为Fout=(Fx-tal÷2)×2M÷N,即Fout=Fxtal×M÷N。其中M为PLL的环路分频系数,N为输出时钟的分频系数,二进制的N为00,01,10,11时分别对应的分频系数为1,2,4,8。选用10MHz晶振,因为PLL的最低频率为400MHz,则Fout=10×M÷N,根据AD芯片的采样率范围,选择N=“11”,输出频率范围为50Hz~l00MHz,可选的频率间隔为1.25MHz,选择M=48,便可使输出频率为60MHz。

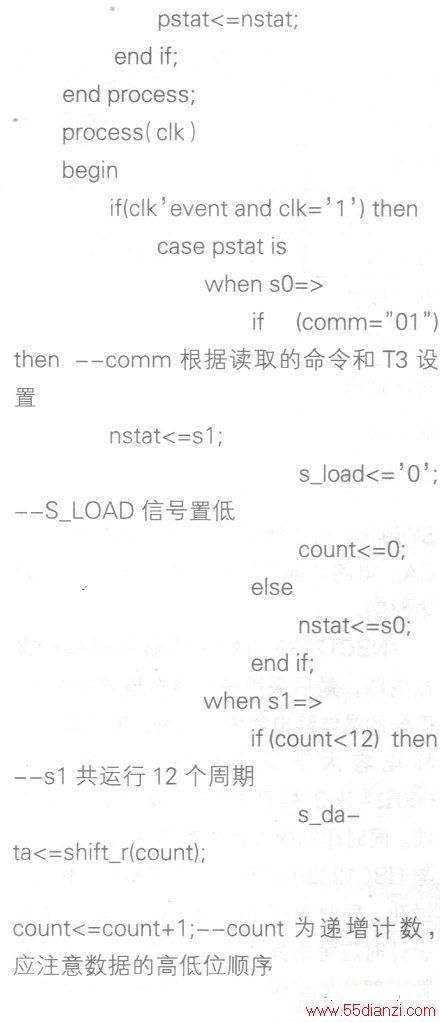

NBC12439可通过并口或串口实现配置,并口通过采集输入引脚M[6:0]和N[1:0]的状态实现,在/P_LOAD上升沿转换有效。串口配置通过s_data,s_clks_load三个信号实现,在s_clk上升沿采样s_data并存入到12位的移位寄存器中,移位计算器的组织为3位测试位T2[2:O],2.位输出分频控制位N1[1:O]和7位PLL环路控制计数位M6[6:0],测试引脚TEST的输出由T2[2:O]决定,如下表所示,串口配置的时序如下图。

由上表可见串行配置模式具有并行模式没有的调试功能,如T2[2:O]=110,此时PLL旁路,此时的输出为配置时钟s_clk经N[l:0]分频后的输出频率。所以采用串行配置模式。

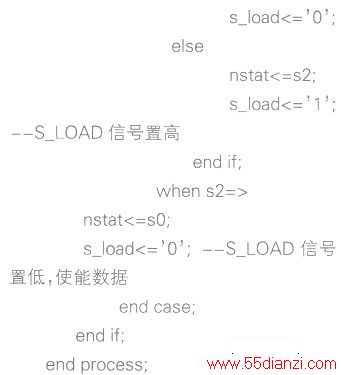

串行配置时/P_LOAD应为高,通过移位寄存器实现12位数据,分别是3位T3,两位N2,7位M7。NBC12439的配置接口通过FPGA实现,三线接口的时序, FPGA通过状态机程序实现时序要求,通过VHDL语言编写,主要代码如下:

上一篇:利用压敏电阻延时器的电原理图