3 版图设计

使用0.18 μm CMOS工艺技术,对图4电路设计版图。与一般的低压CMOS四象限模拟乘法器电路(图1)相比,版图设计时最显著的提升就是节约4个电阻的版图面积,如果工艺中包含高阻值的电阻类型,这种优势就更为突出。

4 结语

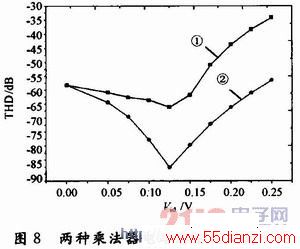

本文提出了一种结构简单的高线性CMOS四象限模拟乘法器,该乘法器基于交叉耦合平方电路结构并采用减法电路来实现。HSPICE仿真结果显示,该乘法器功耗可低至80μW,其线性输入范围达到±0.3 V,-3 dB带宽可达到1 GHz。在同样的电源电压和功耗条件下,相比于图1所示的乘法器,最突出的优点是线性度得到显著改善。在要求低高线性的高频模拟信号处理系统中该乘法器有望得到广泛应用。

本文关键字:暂无联系方式运算放大器,单元电路 - 运算放大器