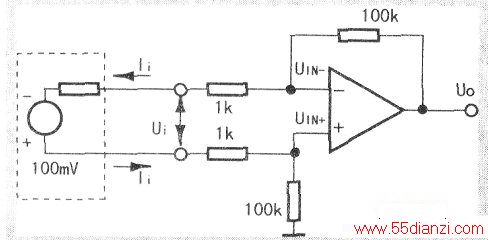

(2)假定信号源的内阻为8kQ,如下图所示。

由“虚短”有UIN+=UIN,则信号输入回路总电阻为8kΩ+1kΩ+1kΩ=10kΩ,。100mV的信号将产生10 μA信号电流、并在内阻上造成80rnV的压降,而真正送到放大器输入端的差模信号Uo只剩下20mmV,即有80%的信号被信号源内阻“吃”掉了。若放大器的内阻趋于无穷大,使信号电流趋于零。不仅对传感器干扰小,且100mV信号可全部作为Ui送入放大器。

(3)若输入电阻小的影响仅仅是信号被衰减倒不可怕,只要相应提高放大器的增益即可补偿过来。讨厌的是在压力不变、传感器信号源电势100mV不变的情况下,仅仅温度变化致使传感器内阻变化时,由上图可看出放大器输入端电压Ui将随温度变化,并造成电路的温漂而大大降低了系统的精度。

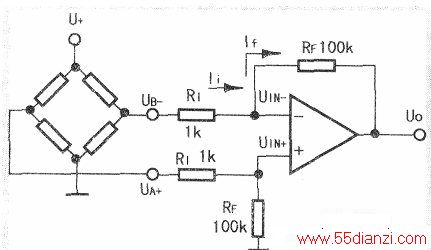

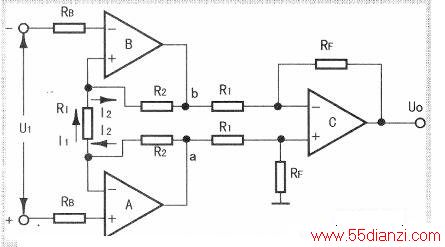

综上所述,具有高输入阻抗的差动放大器才是我们更感兴趣的。下图示由三个集成运放组成的放大器就是具有这种特点的电路。

运放A、B组成差动输入、差动输出的第一级放大器。A、B均采用同相输入方式。由于“虚断”,故有极高的输入电阻(可认为近似等于无穷大)。

由“虚断”及“虚短”可看出R1两端压降即为输

电路抑制共模信号。因为在差动信号Ui=0而具有共模信号时,由“虚短”、“虚断”可推出第一级差放输出端a、b将与输入端等电位,即共模信号将1:1地送到a、b端。因此设计这种电路时应遵循如下原则:

①运放C应选用高共模抑制比(KCMR)的运放。

②运放A、B的参数(主要指失调电压UIO、失调电流IIO及其漂移αUI0、αIIO)应尽可能对称。

③所有匹配电阻阻值和温度系数应尽可能相等。

④所需的电压增益应尽量由第一级差放承担,以提高仪表放大器的共模抑制比。

掌握了集成运放电路的基本分析和计算方法,再根据应用电路的具体要求,就可以灵活地选择不同输入方式和不同结构的电路,并计算出所需电阻的阻值及精度要求。

本文关键字:技巧 运算放大器,单元电路 - 运算放大器

上一篇:基于运算放大器实现的混频器