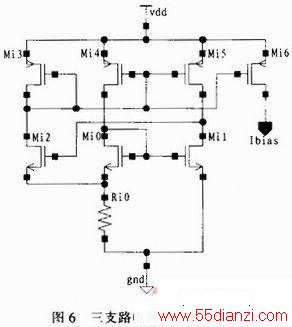

此结构由于节点电压成负反馈,拥有更高的PSRR。该基准电流源的输出电流为:

![]()

可以看出:其输出电流与系统的电源电压无关而只与调节电阻Rs有关,通过调节合适的Rs的阻值,即可得到精确的基准电流。故本文采用三支路电路基准源的设计,而偏置电路采用低压宽摆幅共源共栅结构。

2 仿真结果

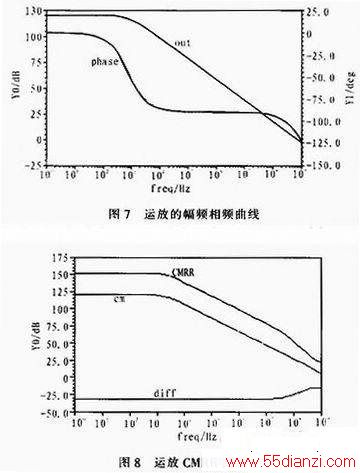

采用SMIC 0.25μm CMOS工艺模型,在Cadence环境下对电路进行SpeCTRe仿真,2.5 V单电源供电,模拟结果显示:运放的直流增益为124 dB,单位增益带宽为720 MHz,相位裕度64°CMRR高达153dB。

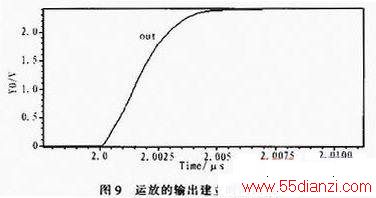

运放的瞬态建立特性如图9所示,于输入端2μs处加2.5 V的阶跃响应,由输出波形测得转换速率885 V/μs;达到0.1%的稳定精度的建立时间为4ns。

图10是运算放大器的版图,通过了DRC与LVS验证,结果显示性能良好。

3 结论

文中提出了一种可用于高速Pipelined ADC中的前置放大器,结合开关电容共模反馈与三支路共源共栅基准电流源等技术,详细分析了增益提高技术的设计原理、弊端及改进方法,实现了一个全差分带增益提升级的折叠式CMOS运算放大器。仿真结果表明:该运放的直流增益达到124 dB,单位增益带宽720 MHz,达刮0.1%精度建立时间为4 ns,转换速率高达885 V/μs。性能良好,满足系统设计要求。

本文关键字:放大器 运算放大器,单元电路 - 运算放大器