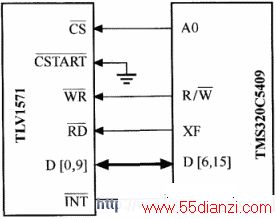

图7 TLV1571与DSP54O9的连接

TLV157l的调试,主要步骤如下:

(1)DSP选通TLV1571,根据图7的连接,将DSP的A0引脚置低,从而选通 TLV1571。

(2)DSP初始化TLV1571的两个控制寄存器,通过DSP的R/ W信号和数据总线初始化控制寄存器。

(3)DSP接收TLV1517的中断信号,进入中断服务程序。

(4)DSP在中断服务程序中,读取TLV1571的采样数据,并保存。

(5)重复步骤(3)和(4),读取下一个采样数据,并保存。

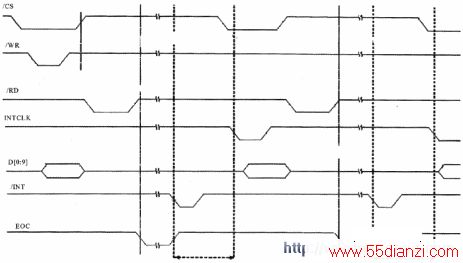

TLV1571各种信号的时序如图8所示。

图8 TLV1571的读写时序

图8是TLV1571的读写时序图。从图中可以看出,对于TLV1571的具体操作如下:

(1)DSP选通TLV1571置信号CS为低),同时写入两个寄存器的值到TLV1571(置WR为低)。

(2)等待TLV1571产生中断信号(INT信号产生下降沿),一般在初始化之后的6个时钟周期后才会有第一次中断信号产生。

(3)DSP响应TLV1571的中断,读入数据到其内部存储器,数据读完后DSP通知TLV1571,TLV1571得到读入完成信号(RD引脚电平为低)后,开始下一次采样。

在响应中断过程中,TLV1571留出6个指令周期等待DSP读数据,直到DSP收到RD为低信号,TLV1571才开始下一次采样。

在对TLV1571读或写的同时,必须保证TLVl571的CS为低,同时还必须保证其他外部I/O空间的片选信号为高(如果系统还有其他外部I/O空间),从而避免将数据写到其他外部设各中。

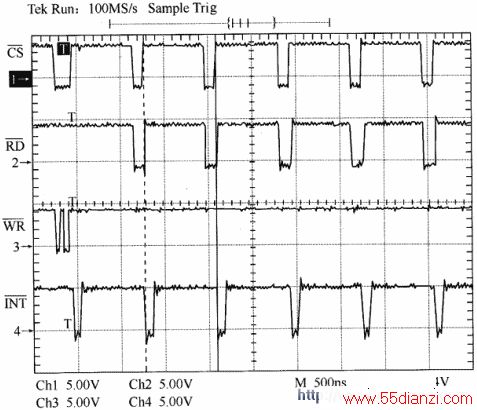

图9 TLV1571的实际运行时序

图9是实际中对TLV1571操作产生的信号波形。WR信号开始有两个下降沿,其目的是为了设置TLV1571的两个控制寄存器。之后,WR信号不再有下降沿,除非再次改变TLV1571的设置。紧接着TLV1571的中断信号产生,即图中的INT的下降沿。此时TLV1571已经完成第一次AD转换,数据已经送到数据线上,INT的下降沿通知DSP可以读人数据。DSP读入数据后,置RD为低,TLV1571收到RD为低后开始下一次采样。

本文关键字:暂无联系方式元器件特点及应用,元器件介绍 - 元器件特点及应用

上一篇:AD5791简介及应用