VerilogHDL综合性设计

1 时钟安排

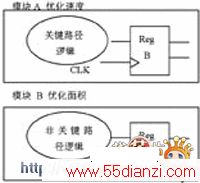

选用上升沿触发的单时钟信号,尽量不使用混合触发的时钟信号。因为时钟周期在时序分析的过程中是关键问题,它还影响到时钟的频率。使用简单的时钟结构利于时钟信号的分析和保持,避免在时钟信号上添加buffer,还利于得到更好的综合结果。图1给出了上升沿触发的单时钟信号结构。

尽量避免使用门控时钟。时钟门控 电路 通常与工艺和时序有关,错误的时序关系会导致错误的时钟和脉冲干扰。时钟的skew会导致hold time的混乱,如图2所示。此外,门控时钟会使设计的可测试性下降。

同时,要避免使用内部的寄生时钟和寄生reset。寄生时钟不能作为扫描链的一部分,所以会使设计的可测试性下降,综合约束的设计难度提高。只有一些低功耗的设计需要门控时钟,在顶层模块中注意要把时钟或reset电路作为分立模块。

2 综合代码

使用可综合的代码可以提高电路的可测试性,简化静态时序分析,使门级的电路和初始的寄存器级代码功能一致。

利用寄存器代替组合逻辑的反馈,避免使用锁存器(Latches)。寄存器受到时序逻辑的青睐,它可以维持一致性和综合的正确性。在设计中用reset信号来初始化寄存器的信号。在Verilog中不要使用initial语句对信号进行初始化。

在每个always块中,指定完整的敏感信号列表。如果不指定完整的敏感信号,行为级的前端综合和后端综合网表的结果会不符。综合工具在elaborate设计时会给出警告。若增加多余的敏感信号则会降低仿真的速度。另外,注意阻塞性赋值和非阻塞性赋值的问题,阻塞性赋值一般用于时序电路中。

Case语句相当于一个单层的多路器;If-then-else语句相当于一个层叠的组合多路器。单一多路器的速度会快一些,所以通常建议使用case语句。避免使用full-case 和parallel_case,这两种语句会导致在仿真和综合过程中代码的解释出现差异。

编写时序逻辑的代码要包括状态机和一个时序的进程,通过在进程外用assign语句来生成复杂的内部中间变量从而改进代码的可读性。使用define语句来定义状态向量。把有限状态机和非有限状态机放在不同的模块中有利于综合。

在RTL代码中不要使用任何延迟常量。延迟量不仅会导致在一些环境中的不正确,还会使得仿真和综合的结果不一致,扰乱RTL 仿真器 代码的优化。

3 代码划分

为了得到更好的综合结果,更快的综合速度,用简单的综合策略来满足时序的要求,推荐使用以下综合划分的技术。

● 所有模块都使用寄存器输出。对于每个设计的子模块都要记录所有的输出信号,这样可以简化综合的过程并可预测输出的驱动能力和输入的延迟。

● 把局部的相关联的组合逻辑放到同一个模块中,对于有不同目标的设计应放在不同的模块中。例如在综合的过程中,把需要优化面积和速度的关键路径逻辑放在分开的两个模块中,如图3所示。

● 综合时间的划分最主要的标准是逻辑功能、设计目标、时序和面积的需要。准确的时序计算和适当的约束对综合时间的影响远远大于电路规模的影响。把同一设计目标的电路逻辑放到一起也会减少综合时间,而设计的约束过多会增加综合时间。减少综合时间的关键是在设计之前制定精确的时间预算,并使设计的宏模块达到预算的要求,然后编写综合约束来满足预算,最后是运用综合工具的命令来实现约束。

● 避免时序异常。时序异常主要包括multicycle path和false path。如果设计中一定要用到多周期路径,应记录开始和结束点来确保在芯片级的有效。尽量避免使用异步逻辑,异步逻辑会给设计的正确性和验证带来困难。

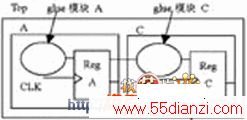

● 注意glue模块的放置。将顶层的连接模块放到底层模块中,同时确保顶层含有I/O管脚和时钟 发生器 ,如图4所示。

HDTV芯片的特点

所设计的芯片应用了数量众多的不同类型的RAM,其中包括内部1个单口RAM、2个双口RAM、3个ROM和20个寄存器堆栈。

芯片内部要求多时钟信号(27MHz、74MHz、150MHz),并通过clock mux来选中时钟。27MHz时钟用于dma模块中的PCI 总线 时钟,同时它和74MHz时钟通过模式选择来确定是HDTV模式还是SDTV模式的解码。Pll核心时钟频率为13.5MHz,Pll输入时钟经过11倍频后产生148.5MHz时钟,pll时钟同时也用于测试。此外还有6个驱动外部芯片的输出时钟,即PCI时钟、视频时钟、2个SDRAM时钟和2个SRAM时钟。

为了得到较高的测试覆盖率,本设计使用多种测试方法,如扫描链(scan chain)、边界扫描(boundary scan)和 存储器 的内建自测试(Bist)等。本设计多数模块采用BIST方法达到测试目的,采用的是Mentor Mbistarchitect工具来自动插入BIST代码。其他部分用Mentor Jtag工具来实现边界扫描,插入JTAG代码。

芯片外部与高速的SDRAM和SRAM的连接,每个模块都包括4片RAM。HDTV芯片主要通过sdr_ssr_sel信号来实现两种环境的转换。

如图5所示,HDTV芯片的结构设计方案层次复杂,芯片主要分为三层,其中core_top是不依赖于工艺的,它的主要功能是完成HDTV码流的解码。

如上所述,芯片的这些特点给后端的布局布线提出了很高的要求,综合结果会直接影响布局布线(floorplanning),因此综合的方法很重要。

综合方案

1 初步综合

首先把设计进行粗略的Top-down综合,查看综合结果报表。根据PDK的数据设置基本的Design Rules和Design Constraints。包括Setting Design Environment(Fanout load,Output load,Input drive impedance)和Setting Design Constraints(Design Rules Constraints (max_transition, max_fanout, max_capacitance),Timing Constraint (max_delay, min_delay),Area Constraint)。经过初步综合后延迟的结果如表1所示。

表1给出的slack=-0.94是在没有考虑wireload的情况下的结果,所以还需要很大改进。

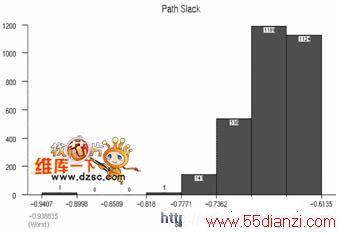

图6是综合后用design_vision对critical path进行统计,得到的path slack分布结果。

2 基本 解决方案

根据上述统计结果,得到core-top模块不满足时序要求的critical path最多,所以要通过把core-top模块单独进行优化来得到更佳的综合结果。首先设置Design Environment和Design Rules,然后对延迟进行优化。

本文关键字:电视 元器件特点及应用,元器件介绍 - 元器件特点及应用

上一篇:芯片设计中的IP技术