2.5 布线与芯片完成

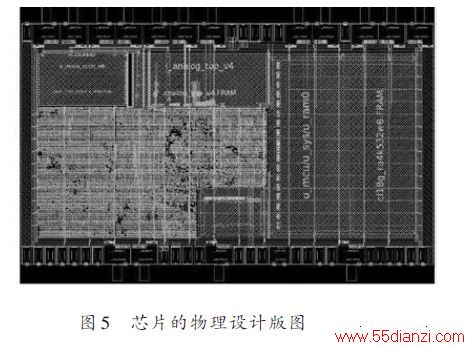

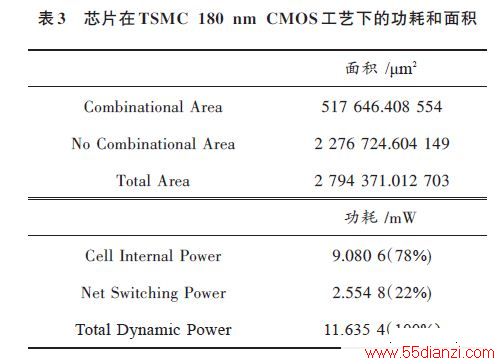

本文将布线及其优化分开来做,首先在初始布线阶段完成全局布线(global routing)、详细布线(detail rout-ing)和检查与修正(search&repair),然后采用拓扑算法对布线进行优化,同时对电流漏功耗进行优化。为了防止天线效应的发生,在芯片完成阶段对芯片进行了天线效应修复设计,此时芯片中依然存在空白区域,需要填充filer 以满足DRC 的要求。图5 是该芯片的物理设计版图,表3 是该芯片的面积与功耗,可见总面积为2 794 371.012 703 μm2,总功耗为11.635 4 mW.经过仿真后证明芯片于50 MHz时钟频率下正常工作,满足设计要求,证明本次设计是正确有效的。

3 结语

本文基于TSMC 180 nm 工艺完成了一款用于无线火灾监测系统中的微处理器芯片的物理设计,采用不同策略分别完成芯片的布图规划、布局、时钟树综合及布线等设计步骤后得到了该芯片的版图及面积、功耗等报表,物理设计后芯片的各项设计指标均满足设计要求,证明了该芯片物理设计的正确性。

上一篇:单片机在金箔定位系统中的应用