* 检查如图1所示的 PCB 设计目录结构是否有效。

* 可以运行后端封装程序(如应用于ViewDraw的pcbfwd)。该程序可检测一些违反规则的设计缺陷(如网路名称的数目和类型特性),而这通常很难采用DRC工具检测。此外,还能赋值给那些尚未赋值的符号参考标志符特性 (如R4)。

* 检测2.0.1节中讨论的输入文件是否存在,并将其注入DRC。

* 找到PCB设计名称并将其注入DRC。

* 将其输出文件的路径和名称注入DRC。

* 建立所需的工具环境变量,如用于ViewDraw和ViewBase的WDIR。

* 调用DRC程序。

* 按需求打印帮助信息。

* 打印用户和运行时间信息。

* 执行后处理。这既可以像修正控制工具检测DRC输出文件那样简单,也可以像主动处理DRC输出文件那样复杂(如从其它数据源添加更多的信息或执行排序操作)。C或许不是最佳的数据排序或文件分析工具,因为如果按数字顺序排列文件,采用UNIX排序命令更为简单:sort +1n source_file > sorted_file。

DRC开发:main()函数

可以调用DRC程序drc.c,该文件具有两个主要函数:drc_net()和drc_inst()。drc_net()遍历了全部网路而drc_inst()则遍历所有的元件(符号),这样就能检测任何有违规则的设计缺陷。这两个函数都能产生附属的输出文件,可以参见1.0 节和4.0节。

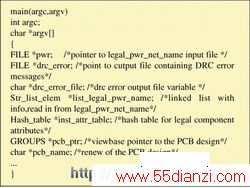

drc.c首先应当包含全部由C、ViewBase和用户创建的头文件,如stdio.h、viewbase.h和 viewbase.h。现在可以设定drc.c接收输入参数,这样不仅能为输入和输出文件声明变量和文件指针,还可使ViewBase指向 ViewDraw数据库,并创建链接列表和散列表以存取从输入文件读入的信息。下面给出了main()函数的部分代码实现。

当DRC封装程序激活DRC时,将导入输入和输出文件名及PCB设计名 (参见3.0.1节)。数据结构Str_list_elem和Hash_table定义在drc.c包含的头文件中,而GROUPS则是ViewBase数据类型。

下一步,main()函数可以通过检验argc的取值从而确保输入参数数目正确。如果参数值正确,那么将为变量分配正确的输入参数。

此时,main()函数可以初始化ViewBase数据结构,并使ViewBase指针pcb-ptr指向PCB设计。如果该设计存在并有效,那么main()函数应当:

* 打开全部输入文件,读取信息并将信息存储到内部数据结构(如Str_list_elem和Hash_table)中, 然后关闭输入文件。

* 打开所有输出文件以写入信息,这些文件可以是设计规则错误/警告文件,也可以是附属文件。

* 调用drc_net()和drc_inst()函数执行实际操作。

* 关闭所有输出文件。

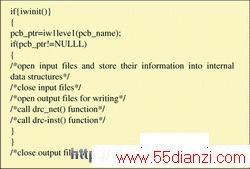

main()函数中完成上述功能的C和ViewBase代码如下:

[列表3]

这里,iwinit()和iw1level()是ViewBase例程。前者初始化全部载入例程(这也是必须的),而后者则载入整个PCB设计。为了保证只载入一张电路图,可以调用iw1sheet()例程(本文的DRC工具并不使用该例程)。需要注意的是,正确的设计指针、文件指针、链接列表、变量名称等必须传入drc_net()和drc_inst()函数:

drc_inst(pcb_ptr, pcb_name, drc_error, list_legal_pwr_name, ...);

drc_inst(pcb_ptr, pcb_name, drc_error, list_legal_pwr_name, ...);

www.55dianzi.com

如果设计采用分层结构及不同的器件符号,那么还必须确保 DRC 能正确处理这些器件。

DRC开发:drc_net()函数

drc_net()在 PCB 设计中遍历所有网路并检测任何违反设计规则的故障,然后创建附属的输出文件。实现上述功能的基本代码如下:

[列表4]

这里,iggrpnet()和ignetnxt()函数是在PCB设计中检查每个网路的ViewBase 例程。ignetnam()函数也是检查网路名称的ViewBase例程。ViewBase中的数据类型包括NETS、PINS、COMPONENTS、 SYMBOLS和ATTRIBUTES。drc_net()函数可检测下述违反设计规则的错误:

* 非法网路名。如果网路名由ViewDraw自动分配,那么将具有如下格式:$#...#N#...#,第一个#...#表示图表编号,第二个#...#则表示网路号。PCB设计人员指定的网路名必须以字母开头,其后的字符数不多于30。

drc_net()函数应调用legal_net_name()函数执行该任务。在UNIX系统中,利用包含在DRC程序中的regexp.h头文件可以极大地简化采用C语言编写的常规表达式匹配/校验程序。drc_net()应将网路名称变量和违反设计规则的文件指针存储在 legal_net_name()函数中,该函数具有如下形式:

[列表5]

后端封装工具pcbfwd也可检测非法网路名,但其功能受限于简单的常规表达式。上述代码可处理任何常规表达式,同样地,如何在运行pcbfwd工具之前或之后找到非法网路名称也需要权衡。对于简单的网路名称,可以使用pcbfwd。

* 网路上的总线竞争也是严重问题。总线竞争有两类:一类是图腾柱输出间的总线竞争,而另一类则是图腾柱与三态输出间的总线竞争。基本代码实现如下所示:

[列表6]

这里,ignetpin()和igpinnnx()函数是在网路上检查每个引脚的ViewBase例程。 igpinown()例程返回引脚实例(系主)指针。函数get_inst_attr()、get_pin_attr() 和get_sheet_num()则返回请求实例属性(参考标志符REFDES)、引脚属性(PINTYPE)及引脚实例所在的图表编号。 get_pin_attr()函数的基本代码如下:

[列表7]

get_inst_attr()函数的基本代码如下:

[列表8]

get_sheet_num()函数的基本代码如下:

[列表9]

* POWER和GROUND网路中的非法名称。这些名称将与存储在内部数据结构中的信息(如链接列表)进行比较。

* 报告那些具有负载但不具有驱动程序或者具有驱动程序但不具有负载的网路。这可以通过标注网路上每个引脚的类型加以实现。网路应当带有1个输出引脚或多个三态输出引脚及最少一个输入引脚,此外还可提供与网路全部器件和引脚相关的参考标志符和符号。

* 报告那些不带上拉电阻或所带上拉电阻未连接到POWER的所有集电极开路输出。

* 一旦网路的负载超过常规数目(良好的信号完整性条件下限额为8),那么将打印警告信息。

DRC开发:drc_inst()函数

drc_inst()函数与drc_net()函数类似,不同的是,前者遍历了全部电路图表及PCB设计中电路图表上的所有实例,从而检测违反规则的设计缺陷或创建附属的输出文件。其代码实现如下:

[列表10]

上面关于drc_net()函数的讨论提供了充分的C和ViewBase代码示例,这里就不在赘述。下面给出了drc_inst()函数可检测的部分违反规则的设计缺陷:

* 非法或遗漏的符号库混淆。PCB设计中的所有符号必须来自共同符号库,使用来自错误符号库的符号是一个极为常见的错误,尤其是对于那些只依赖于符号进行设计的后端处理工具。

* 遗失符号和/或引脚属性,例如那些描述器件几何结构和引脚类型(in、out、bi和tri)的特性。

* 非法的符号和/或引脚属性。例如,引脚类型可具有IN值,但不包括INPUT值。这将对后端封装工具(如pcbfwd)如何为布线工具(如Allegro)提供信息产生影响。

* 符号上的参考标志符值,尤其是对于串行器件(如电阻、电容和电感)。大多数信号完整性工具需要这些器件以字母R、C和L开头,因此可将这些器件作为串联元件而非离散器件进行分析。类似地,drc_inst()函数可将其值同描述的属性进行对比以保证两者完全匹配。

* 非法去耦电容。这可能导致POWER线dv/dt问题。* 非法上拉和下拉电阻。

www.55dianzi.com

* 不与符号POWER或GROUND平面相连的POWER或GROUND引脚。

* 未使用的输入引脚不被电阻上拉或下拉,或者该电阻不与POWER或GROUND网路直接相连。

* 当单个电阻器上拉或下拉1个以上输入引脚时发出警告信息。

* 对于直接与POWER或GROUND网路相连的非专用POWER和GROUND引脚发出警告信息。

如果采用了标记技术,那么将检验该标记是否注明了正确的可选器件,例如型号是否有效及其几何结构是否与默认的器件规格匹配。

DRC 不应当具备的功能

尽管DRC能够实现很多功能,但仍然可以采用其它方法以期更好更便捷地加以实现。后端封装工具可为布线工具封装 PCB 设计,因此可提供有效帮助。在ViewDraw中,pcbfwd可用来检测诸多违反规则的设计缺陷和设计错误。

DRC和pcbfwd可检测的问题之间存在重叠,因此何时检测何种设计问题就需要进行折衷考虑。DRC通常在设计完成之后及 pcbfwd运行之前才能正确地运行。理想情况下,运行pcbfwd只为了封装设计,因此更多的DRC可以得到更好的检测结果。但设计人员仍然需要在其投入精力开发具有超强功能的DRC与pcbfwd现有的免费功能之间取得平衡。这一节简单地讨论了这些问题。

pcbfwd由配置文件控制,如果布线工具为Allegro,那么配置文件名为allegro.cfg。配置文件中的 BeginChkRules - EndChkRules部分可用来检测众多错误,如相同符号的重复属性、非法网路和网路属性名称、损坏的异质封装、异质符号上的冲突属性及遗漏属性。例如,为了在异质符号上获取冲突的属性,可以在allegro.cfg文件中添加如下内容:

本文关键字:暂无联系方式综合-其它,单片机-工控设备 - 综合-其它