HKMG技术未来一段时间内的发展趋势:

High-k绝缘层的材料选择方面,包括Intel公司的Bohr在内,大家似乎都同意HfO2将在未来一段时间内继续被用作High-K层的材料,业界近期将继续在改良HfO2材料上做文章,部分厂商可能还会考虑往HfO2层中添加一些特殊的材料,但他们近期不会把主要的精力放在开发介电常数更高的材料方面。

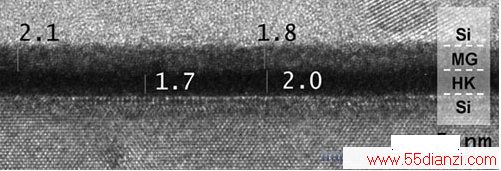

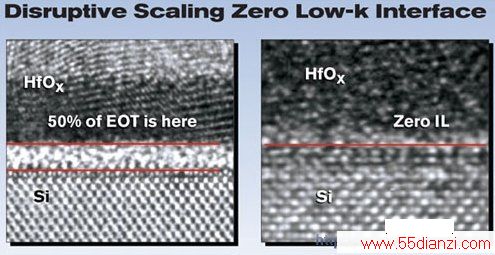

另外,有部分厂商的主要精力则会放在如何减小High-k层下面的SiO2界面层(IL)的厚度方面,其目标是在High-k绝缘层的等效氧化物厚度为10埃时能把这种界面层的厚度降低到5埃左右。Sematech公司负责High-k项目研究的高管PaulKirsch表示:“业内现在考虑较多的主要是如何进一步优化HfO2材料,而不是再花上五年去开发一种新的High-k材料。从开发时间要求和有效性要求方面考虑,目前最有意义的思路是考虑如何消除SiO2界面层和改善High-K绝缘层的介电常数值。”

Gatefirst在如何有效消除SiO2界面层(ZIL)方面的优势及各方评述:

消除SiO2界面层方面,在去年12月份举办的IEDM会议上,科学家们发布了多篇有关如何消除SiO2界面层的文章(ZIL:zerointerfacelayer),其中IBM的Fishkill技术联盟也公布了自己的方案,并宣称这种方案将在自己的gate-first32/28nm制程中使用。

耶鲁大学的T.P.Ma教授表示,ZIL技术虽然非常吸引人,但通常需要使用高温工步来消除SiO2界面层,而gate-first工艺制作的栅极则正好能够承受这种高温,所以这项技术对采用gate-first工艺的厂商比较有利。他认为,按照他的理解,ZIL技术的实现需要使用“高温化学反应”来有效地去除栅极结构中残留的SiO2界面层,这样这项工艺对使用gate-first工艺的厂家而言实现起来难度更小一些,而使用gate-last工艺的厂商则会尽量避免使用高温工步。他还表示,IBM和Sematech公司所制出的ZIL结构已经能够在5埃的等效氧化层厚度条件下达到较好的防漏电性能。

不过据Sematech公司的材料与新兴科技研发副总裁RajJammy表示,尽管Sematech公司早期的ZIL结构确实是在gatefirst工艺的基础上制造出来的,但是“要制出ZIL未必需要依靠高温处理工步,而主要是要去掉界面层中的氧离子。”他还强调不同的情况需要采用不同的热处理方式来进行处理,才能得到较好的管子参数。

而另外一篇IMEC的研究报告则指出,“我们制作ZIF的方法是需要进行高温热处理的,不过要生成理想的无界面层栅极结构的方法有很多种,因此未必说gatelast工艺就不利于ZIL的制作。”他还表示应该可以找到一种方案来兼顾ZIL与gatelast工艺的优点。

另外,在被问及对ZIL技术的看法时,Intel高管Bohr回答称,“在我的印象中这种技术并不是很有效,这主要是由于ZIL结构对沟道的载流子迁移率有一定的不良影响,而如果我们能够很好地控制界面层的材料和厚度,管子的性能一样也可以达到要求”,他还表示“相比之下,我认为我们应该努力去改善High-K绝缘层的材料,并想办法减小金属电极的电容.”

Gartner市调公司

www.55dianzi.com

的Freeman则表示,从28nm制程节点开始,台积电公司与GlobalFoundries之间的 HKMG 产品由于所用的工艺不同,因此将存在比较明显的区别。按照这样的差别趋势发展下去,一种最终的可能就是IBM和GlobalFoundries会在22nm制程节点马上转向 Gate-last 工艺,而另外一种可能就是由于gatefirst在ZIL方面的优势被实际的应用证明,而将慢慢处于领先的位置。Freeman还表示:“在16nm制程节点,如何控制好管子的界面层,将是至关重要的。”

本文关键字:暂无联系方式综合-其它,单片机-工控设备 - 综合-其它