2.4 基于ChipScope Pro的FPGA调试技术

新一代FPGA器件所具有的规模、速度和板级要求使得利用传统逻辑分析方法来调试采用FPGA器件进行的设计几乎是不可能的。CS和BGA封装无法提供进行物理探测用的外露引脚。为了解决这些问题,Xilinx公司推出了ChipScope Pro 片内逻辑分析仪解决方案。基于开创性的ChipScope ILA产品,ChipScope Pro实际上是将逻辑分析仪(ILA)和总线分析仪(IBA)核心嵌入到了您的设计中。这些嵌入核心允许用户观察所使用的FPGA器件中的所有内部信号和结点,此外还包括对业界领先的Virtex-II Pro™ FGPA 器件内所集成的IBM PowerPC 405处理器的IBM CoreConnect片上外设总线的分析支持。

ChipScope Pro主要包含以下几个核心部件:

(1) ChipScope Pro核心生成器:为综合控制器(ICON)核心、CoreConnect™ OPB的总线分析核心(IBA/OPB)、逻辑分析(ILA)核心及安捷伦跟踪核心(ILA/ATC)提供网表和实例化的模板;

(2) ChipScope Pro核心插入器:自动地为用户已经综合完的设计中插入ICON、ILA和ILA/ATC的核心;

(3) ChipScope Pro分析仪软件:提供器件的配置、触发的设定和ILA、IBA/OPB及ILA/ATC核的踪迹显示功能。各种核心实现了信号的触发和捕获,而ICON核心专门用于与边界扫描(Boundary SCAN)管脚的通信。

ChipScope Pro分析仪软件支持所有通过JTAG边界扫描链连接PC与器件的下载电缆,如Xilinx的并口电缆 Cable III、Cable IV和依元素提供的利刃系列下载调试电缆等。

用户可以使用ChipScope Pro 核心生成器生成的例示代码插入HDL源程序中,从而将ICON、ILA等核心插入到他们的设计中。当然,你也可以使用ChipScope Pro核心插入器将ICON、ILA等核心直接插入到已经综合完成的设计网表中。然后,利用Xilinx ISE 5.2i的综合工具进行综合布线,生成配置文件。这样用户就可以通过ChipScope Pro分析仪软件将配置数据流下载到待测的器件中,进行分析测试。

3. IP Core设计及其在SOPC中的应用

3.1 IP资源复用与IP Core设计方法

由于芯片设计的复杂性和产品面市时间对于保证终端市场的成功率至关重要,设计师不断寻求缩短设计周期的方法,以及更有效的设计方式。随着我们步入系统级芯片时代,利用IP内核和可编程逻辑进行设计复用显得日趋重要。IP资源复用(IP Reuse)是指在集成电路设计过程中,通过继承、共享或购买所需的智力产权内核,然后再利用EDA工具进行设计、综合和验证,从而加速流片设计过程,降低开发风险。IP Reuse已逐渐成为现代集成电路设计的重要手段,在日新月异的各种应用需求面前,超大规模集成电路设计时代正步入一个IP整合的时代。

IP Core是IP Reuse的载体和核心内容,基于应用需求、规范协议和行业标准的不同,IP Core的内容也是千差万别的。但是,为了使IP Core易于访问和易于集成,其设计必须遵循一定的规范和准则。 在IP Core的开发方面,许多开放性的团体都付出了巨大的努力来推动各种IP Core的开发和IP Reuse理念的 推广,其中比较著名的是Open Cores开发组织( http://www.opencores.org )。他们不仅开发了许多开放源代码的IP Core,涵盖了处理器IP、处理器外设控制器IP、算术运算单元IP、DSP算法IP等方面,而且编写了详细的IP Core编码风格和项目模板。国内开放性团体IP Core开发小组( http://www.IPcore.com.cn )也在IP Core开发和IP Reuse理念的推广和普及方面进行了不懈努力。

编码风格(Coding Style)是基于HDL的IP Core源码编写的指导性文档,其可读性直接关系到IP Core的易于访问和易于集成性。编码风格一般包含几个方面的约定:文件头和版本说明、联机注释、命名规则、可综合编码等。

项目模板则规定了完成一个IP Core设计包含的主要内容及所需提供的文档,项目模板内容及其文档直接关系到IP Core的易于集成特性,一个IP Core必须是完整的、经过全面验证的,才能顺利地集成到应用项目中去。项目模板一般包含几个方面的内容:项目定义、接口说明、系统结构和模块、设计文档说明、测试验证报告、约束和实现、版本说明、试用评价以及参考文献等。

3.2 IP Core验证:仿真、测试与评估板

IP Core设计在完成编码阶段以后,对其功能的测试验证是一项非常重要的内容,因为这直接关系到IP Core资源的可用性。仅仅通过功能仿真、时序仿真和测试向量验证的IP Core是不完备的,它必须通过实际系统的验证。国际上各大公司通常采用的办法是评估板验证,也即构建一个与实际系统IP Core应用一致的硬件环境,通过下载 FPGA 配置使其具备相应的逻辑功能,并进行实物仿真,图3是依元素科技开发的专用于 SOPC 和IP Core设计验证的评估板实物照片和原理框图。

4. SOPC设计应用实例:单芯片动态可重构信号处理器

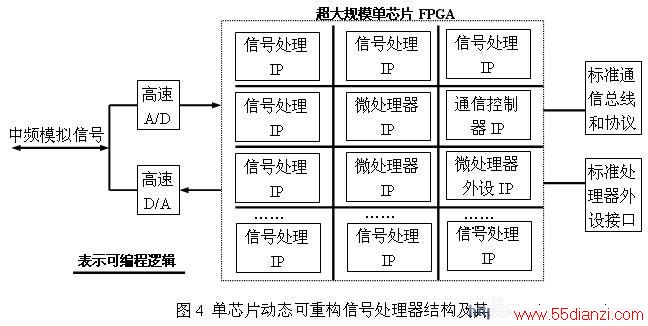

数字信号处理器是一种为高度密集运算量而专门优化的嵌入式处理器,典型的有TI的TMS320系列和AD公司的ADSP,其中TI公司最新产品 TMS32C641X系列处理器工作频率高达1GHz,而处理能力可达数GFLOPS。但是,归根结底,数字信号处理器还是一种基于软件程序顺序执行指令的串行处理器,从微观上看,处理器中某一特定时刻,只有一个算数逻辑单元(MAU)在执行特定的指令,如果要在硬件上实现多个MAU并行,只能通过将多个 DSP器件并行处理,这样必然导致PCB设计及调试方面复杂性的大幅度提高,而且DSP器件之间的藕合程度、处理任务划分与进程间通信等方面的灵活性也存在一定问题。基于可编程逻辑器件实现的 可编程片上系统 设计技术则从很大程度上克服了上述问题,SOPC的处理器IP、控制器IP、信号处理算法IP等各种数字逻辑都是基于可编程逻辑在同一个FPGA芯片内部实现,可以任意添加、裁减以及改变连接关系,而且它们之间的互连方式是比板级PCB互连更具有紧藕合特征的片内互连。

基于SOPC设计技术实现的单芯片动态可重构信号处理器结构及接口如图4所示:

5. 结束语

随着新新一代超大规模可编程逻辑器件工艺的不断进步和开发工具的不断完善,以FPAG为基础的SOPC技术将更加广泛的应用在各个领域,FPGA的将在更广泛的范围普及,成本和价格将不再成为我们拒绝在设计中采用FPGA的理由。我们有理由相信,SOPC、IRL等设计理念将会对我们的设计方式产生新的变革,也必将给每一位嵌入式工程师带来有益的思路和更加宽广的创意空间,从而为更新日益加速的嵌入式产品设计注入新的活力。

本文关键字:技术 综合-其它,单片机-工控设备 - 综合-其它

上一篇:模拟设计与验证工具现状