c. 手动复位,当手动复位信号有效,产生复位,用于调试。

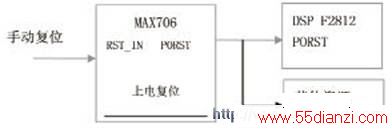

MAX706的复位信号形成F2812的上电复位输入,使系统所有资源复位。复位电路如图7所示。

图7 复位电路

串行总线处理电路

本模块串行数据的接收和发送都采用TL16C554协议芯片来完成,RS422和RS232总线传输通过不同的接口芯片完成电平转换,其功能框图如图8所示。

图8 串行数据功能实现电路

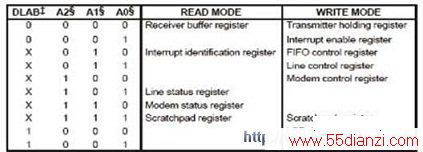

16C554通过对各个寄存器的编程完成串行数据的初始化及传输,在上电初始化时,本模块将串行数据初始化为数据位8位,停止位1位,无奇偶校验位,波特率为115.2KBPS,在完成上电BIT后,主机可通过改变双口存储器的初始化参数来满足自身对串行数据格式的约定,16C554各寄存器地址分配如表3,各个寄存器对应的访问地址为该串行通道分配的基地址加上偏移地址,即:各寄存器访问地址=BASE+[A2A1A0]16。

表3 协议芯片寄存器地址分配

串行协议芯片通过有效的初始化才能实现串行数据的正确接收和发送,在进行初始化的时候确保串行通道没有接收和发送数据。其初始化流程如表4所示。

表4 串行协议芯片初始化

控制逻辑电路

控制逻辑电路负责整个DSP数据处理模块上控制和状态信号的产生,负责PCI总线时序控制和逻辑译码。该逻辑功能由 CPLD 可编程逻辑器件实现,逻辑描述由VHDL语言完成。控制逻辑电路主要完成以下功能:

a. TMS320F2812 总线时序支持电路;

b.系统总线接口时序支持电路;

c.地址译码;

d.地址转换及地址三态控制;

e.实现对数据总线管理逻辑的控制;

f.系统总线复位。

结束语

根据以上原理,我们研制了该 智能接口板 ,通用性强,接口简单,可以满足大多数应用条件,经使用证明设计合理,稳定可靠。