һ̨���������ĵ������ӱ任������ѡ���������Ԫ�����������ĵ�·�⣬ӡˢ��·���������ֺ����������������ȷ�ṹ����Ǿ������ر任���ܷ�ɿ�������һ���ؼ����⡣��ͬһ������Ͳ����ĵ�·���������������ƺ͵�����������IJ�ͬ�������ͬ�Ľ�����������ܴ��ںܴ�IJ��졣���������������ȷ���ӡˢ��·��������ֵĽṹ����ȷѡ���߷������������Ĺ��սṹ�����������������ǡ������Ĺ��սṹ���ȿ��������߲������������������ţ�ͬʱ���������еİ�װ����������ȡ�

����[1]�ӿ����ŵĽǶȽ�����ӡˢ��·�������ϵ�ѡ����Ĵ��������ߡ���������Ƶȡ�����[2]��ϸ�����˿�����ԴPCB�Ű�Ļ���Ҫ�㣬��������һЩʵ�õ�PCB�Ű����ӡ�����[3]�������PCB���·����еĹ�����ƺͿ����ŵ���Ч�����������ȷ���ӡ�Ƶ�·��������ֺ�ѡ���߷���ĸĽ����Ա�����PCB�����Ƹ��ź����������Ҫ������[4]�ڽ�����Ƭ��Ӧ��ϵͳ�ɿ������ģ�͵Ļ����ϣ������PCB�ɿ������Ӧ����������ơ�������ƺ�PCB�ߴ缰�������ã������������PCB�ɿ��ȵķ������������ӱ任�����ղ�Ʒ�ĺû����ںܴ�̶���ȡ��������ƵĿ��ر任��PCB�IJ��ߡ���������û���漰�������ӵ�·�IJ������⡣������Ҫ�������õ������ӵ�·��PCB���ߵļ����ؼ����⣬�����ڿ��ر任������߲ο���

2 �����������ӵ�·

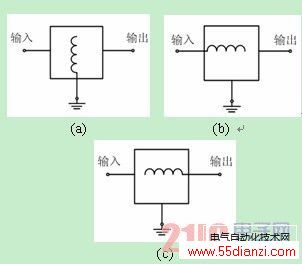

������ĵ������ӵ�·������boost��buck��buck-boost[5-9]������������ȡ���ڵ�е����ӷ�ʽ�����ú��ʵIJο��غ��Եõ�������ͬ�Ķ��ӣ�����ˡ�����˺͵ضˣ���ͼ1��ʾ�������һ�������������õ�buck-boost��·����������������������õ�boost��·����������������������õ�buck��·��

ͼ1 �������ӵ�·���������˽ṹ��(a) buck-boost���ˣ�(b) boost���ˣ�(c) buck���ˡ�

3 ���ؽڵ�

�ڿ���������������֮�����õĵ�е��������ڵ��֮Ϊ���ؽڵ㡣�����ӵ������˽ڵ㣬���ݿ���״̬��ͬ�����뿪�ػ��߶����ܡ��κ�DC-DC�任�����˾��д˽ڵ㣬�ɶ����ܲ��빹�ɵĽڵ�ɷ�ֹ��ĵ�ѹ��������

�ڵ�����ڿ��غͶ�����֮�����ת������˶�������Ҫ�����Ե�ת��״̬�������������ڿ��ص�ͨʱ�ӷ����ѹ������ض��ڼ�������ѹ����ˣ��ڵ��ѹ��������һʾ����̽ͷ�����ڴ˽ڵ㣬̽ͷ�ؽ��ڴ����˵�·�ĵأ����õ�ѹ����Ϊ�������˲������е�ѹ���μ�Ϊ���ƣ���֮ͬ�����ڴ˵�ѹ������ѹ��Χ�ı䣬�ı�����ɵ�·���˾�����

ʵ�����PCBʱ��Ҫ�ر�ע���ֹ�ڿ��ؽڵ㴦������ͭ˿�����������ܳ�Ϊһ����ų����ߣ������ܷ�����Ƶ���ţ�����������մ˸��Ų�ֱ�Ӵ��ݵ������

���м���IC�Ŀ��ؾ�������Ʋ��ַ�װ��һ��������ȻӦ�÷����Ҽ۸���ˣ�����ͨ��������IC����������������������������С�������Ϊ�书�ʼ����ؽڵ���Ǹ�IC������������ţ������Ž����ؽڵ�����ĸ�Ƶ����ֱ�Ӵ��ݵ����Ʋ��֣����¿���ʧ����

4 PCB���ߵĿ��ȡ��������

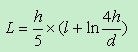

���ڳ���Ϊl��ֱ��Ϊd�ĵ��ߣ�����ֵ����ʽ��1����ʾ��

![]() (1)

(1)

ʽ�У�L��d�ĵ�λ��Ϊcm��

PCB���ߵ�еļ��㹫ʽ�뵼�ߵ�й�ʽ������ʽ��2����ʾ��

![]() (2)

(2)

ʽ�У�ωΪ���߿��ȡ�

��Ҫע�����PCB���ߵ�л����븲ͭ����ء������϶�����ϵ���Կ�������PCB���߳��ȼ���һ�룬������ֵҲ����һ�롣�����߿��ȱ�������10����ʹ���м���һ�롣�����������߿����ô�����Ҫ���ٵ��Ӧʹ���߾����Ķ̡�

�������ʽ��3�����㣬

(3)

(3)

ʽ�У�hΪ������ȣ���λΪmm��һ��h���ڰ��ͨ��Ϊ1.4mm~1.6mm��dΪ����ֱ������λΪmm������1.6mm��ֱ��Ϊ0.4mm�Ĺ����Ϊ1.2nH����Ȼ����ʵ��֤����ҲӰ�쿪��IC�Ĺ������ر�����ʹ��MOSFETʱ����ˣ�����ʹ��һ�����մɵ���ΪIC���һ��Ҫע��õ���Ӧ�����ܿ���IC������PCB���Ӵ��������ڸõ�����IC���ź���֮�䲻���й������ӡ�

��ʵ������ijЩ���ߵĿ��ȶԵ�·���������Dz����ġ����磬��������-�����buck�任�����ӿ��ؽڵ㵽�����ܵ����ߵ�ѹ�DZ仯�ġ��κδ��б䶯��ѹ�ĵ��壬���������������Ĵ�С��ֻҪ��ߴ��㹻��ͻ��γ�E�����ߡ���ˣ�Ӧ�ü��ٿ��ؽڵ㴦����������������������������ΪʲôҪ���ⲻ����“ͭ��”��ԭ��Ψһ�����������ͭ�ĵ�ѹ�ڵ���ǽӵص����ǽӵص㣬�������ߣ����������Դĸ�ߣ��������������Ƶ�������������ط���ЧӦ[10]��

��С��е���÷����Ǽ�С���ȣ����������ӿ��ȡ�������ijЩԭ�����߳��Ȳ��ܽ�һ����С�������ͨ��������ǰ�кͷ������߲��еķ�������С��С����֮���Գ�������Ϊ���Ǵ洢�˴������������������ڴų��С���������������ų���ʧ������Ҳ��ʧ��ͨ����������������ƽ�в��ã��������ǵĵ�����С��ȷ����෴���Ӷ�ʹ�ų����������������ƽ��������PCB��ͬһ����ʱҪ���ķdz�������ʹ��˫��PCB����õİ취�ǽ�����ƽ���������ڰ������������ڲ�����λ�á�Ϊ��ǿ��������ȥ�ų�����Щ����Ӧ�þ�����Щ��

���ڴ������߷���ʽ�任�������β����ߵĵ�лᷴ�䵽һ�β࣬�Ӷ������������һ�ε�Ч©�У�ʹЧ�ʽ��͡���ҪӦ���ϴ�ĵ������貢������������ʱ�����������Ϊ���ء����Կ�������ȥ�ų��ķ�������С��С�

�Ӳ��������Ĺ۵��Ͽ������������ˣ���о������ڹؼ�·������˲��ع���ĵ������IJ��ߡ���Ҫ���ǵ�в����ĵ�ų�������Ӱ�츽���ĵ�·���������ߣ�ͬ����������⡣��ˣ���һ������£����ɱ����������ʹ�����ε�������������⡣��������������Ӧ��������Զ��IC�����ر�ҪԶ�뷴������[11]��

5 �������ӵ�·PCB�ļ����ؼ�����

�ڿ���ת���ڼ䣬ijЩ���ߵĵ�����˲��ֹͣ������һЩ���ߵ���ͬʱ˲�䵼ͨ�����Ǿ��ڿ���ת��ʱ���100ns֮�ڷ�������Щ���߱���Ϊ�ǿ��ر任��PCB���ߵĹؼ����ߡ����ǵIJ���Ӧ�ÿ����̡�ÿ������ת��˲�䣬��Щ�����ж������ܸߵ�di/dt�������·��������ϸС�����͵ĵ�ѹ���[6][7]������Ҫ���ɼ�����в����ĵ�ѹV=L×di/dt����ġ����ݾ��飬ÿӢ�����ߵļ������ԼΪ20nH��MOSFET��BJTת���ٶȸ��ߣ�MOSFET�Ŀ���ת��ʱ��Ϊ10ns~50ns����BJTһ��Ϊ100ns~150ns��������������PCB�ؼ������в������ߵ�di/dt������MOSFET���صı任�������������ӵļ�塣��1����ͭ���߿��أ���30ns�Ŀ���ת��ʱ������1A��˲̬������������0.7V�ļ���ѹ������3A��˲̬��������2����ͭ���ߣ���������4V�ļ���ѹ���������һ���������������ݵ�����/�����Ӱ��任�����ܣ����һ�������IC���Ƶ�Ԫ��ʹ���ƹ���ʧ��ʧ��������ʹ���Ƶ���������ʧЧ�����������Ժ����

������弸���ǹ۲첻���ġ����ȣ����ּ�������һ���̶��ϰ������ռ����������Σ���ʾ����̽ͷ�۲�ʱ��̽ͷ����10pF ~20pF�ĵ���Ҳ�����ո����壬�Ӷ��������κ�������Ϣ�����⣬̽ͷ��Ӧ��̫����������Ŀ���������ʹ�۲�������ȷ���������ĵ�����ʲô��

����buck��buck-boost��·���������Ҳ���ڹؼ�·���С�����ζ������Щ�����й��ʼ���Ҫ�����õ��������װ�á���ˣ����˹��ʼ�����Ҫ�Ĵ����������⣨ͨ���Ǵ���������ݻ��������ݣ�����Ӧ�ڿ��صĵ�Դ����������صĵض�֮�����һС�����մɵ��ݣ�Լ0.1μF~1μF��

����boost��buck-boost��·���������Ҳ���ڹؼ�·���С���ˣ��õ�·���ݺͶ�����Ӧ������������IC���ڸõ������˲���һ���մɵ����������ģ���Ҫ������������·���ȶ���

��buck��·��Ӧע����ȻҪ����������ܾ�������IC/���أ������������ȴû���ϸ�Ҫ��������Ϊ��еĴ���ʹ�ø�·������ƽ��������һ�մɵ�����������ݲ�������ֻ��Ϊ�˽�һ�����������Ƶ����������Ʋ����������������ɿ����ر��Ƕ��ڵ�ѹ����ģʽ����������ݵ�Ч�������裨ESR��ֵ���̫С��С��100m ��ʱ��������ɻ�·���ز��ȶ���

��һƪ����������е�EMC��EMI��ESD