4 比较器失调消除技术

为实现较高的转换速度, 本次设计采用多级比较器结构,由四级低增益放大器和一级锁存器构成, 而高精度的实现需要对比较器进行失调校准技术。比较器的失调电压是由于电路元件的失配造成的, 这种失配通常是随机的, 不能预先估计。失调电压的存在会影响比较器的精度, 在较高分辨率的ADC 中, 输入失调电压不能太大, 这就要使用失调校准技术。失调校准技术在MOS 工艺中是适用的,这是因为MOS 器件的输入电阻近似无限大, 使得晶体管栅极上可以长期贮存电荷, 可以将失调电压贮存在电容上, 通过与输入叠加来消除失调电压的影响。本次设计, 我们采用在每一级放大器加入辅助输入端的方法, 消除比较器的失调。

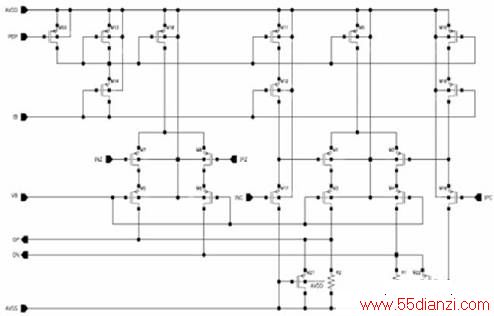

图5 利用辅助输入端消除失调技术

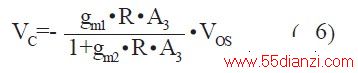

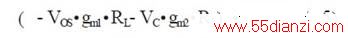

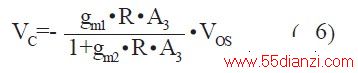

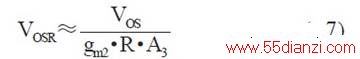

如图5 所示, 主放大器被设计成由两个跨导放大器组成, 由于比较时用于开环, 增益较小, 可用电阻作负载; A3 为反馈环路上的调零放大器, 为高增益放大器。消失调时首先, 开关S1 闭合, S2 将主运放两输入接至共模电平, 此时通过反馈环路, 辅助运放输入端上的电容存储的失调电压设为Vc, 则:

可得:

当S1 断开, S2 接入输入信号时, 比较器正常工作, 由于Vc 的作用, 可以得到此时在比较器输入端的等效失调电压为:

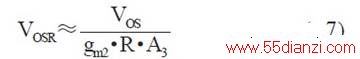

根据ADC 的精度和电容阵列的校准算法, 并通过调节辅助运放和调零运放的增益使多级比较器的精度达到设计要求, 本次设计比较器的精度需高于19 位。图6 为加入辅助输入端的低增益跨导放大器的电路设计, 本次设计各级前放的增益约为22dB.

调零放大器采用全差分折叠式共源共栅结构, 一方面可实现高增益, 另一方面用于构成单位负反馈, 从而可用电容检测并消除自身的失调。本次设计, 该运放增益需要达到70dB 以上, 同时为保证输出共模电平的稳定需加入共模反馈。

图6 前置跨导放大器的电路实现

5 仿真结果

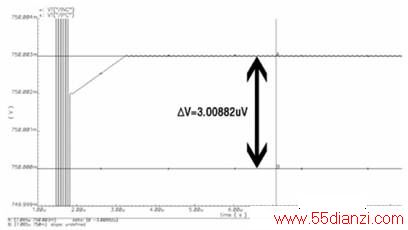

比较器的测试可采用动态失调测试平台( DOTB) 进行,如图7 所示。此方法运用单位增益放大器、积分器的性质, 将比较器接入环路, 通过对测试精度的调整, 最终得到比较器的等效输入失调。

图7 动态失调测试平台框图

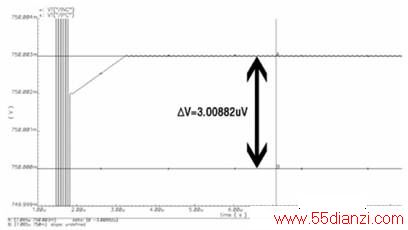

测试结果( 图8) 表明: 加入消失调机制后, 多级比较器等效输入失调约为3μV( <4μV) , 从而使比较器的精度达到了20 位。

图8 单级比较器动态失调测试结果。

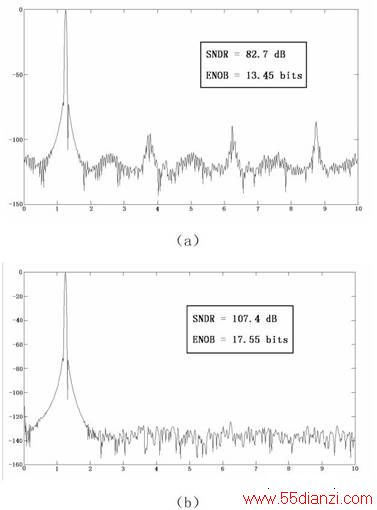

通过对ADC 进行频谱分析, 测量其动态性能,即可反映ADC 的精度与线性度,并验证数字校准的效果。为避免频谱泄漏[7], 加入的正弦激励信号的频率和采样频率应满足如下关系:

Fin、Fs 分别表示输入信号频率和采样频率, Npoint为采样点数, n 为正整数, 且n

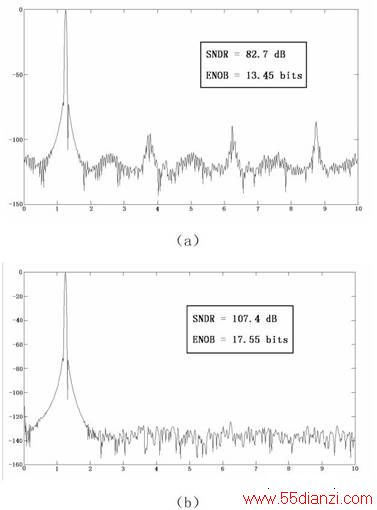

图9 ADC正弦激励下的频谱分析( a) 未校准( b) 校准后。

6 结论

本设计通过由低到高依次校准电容阵列的方法, 改善了电容DAC 的线性度; 利用辅助输入端消失调技术, 将比较器的精度提高到设计所需的指标。

实现了18bit 的精度要求。采用了多级比较器各级一次性消失调的结构, 提高了ADC 的转换速度; 同时, 电容阵列DAC 的设计和运用使得较低的功耗成为本次SARADC 设计的另一优点。

上一页 [1] [2]

本文关键字:转换器 变换电路,单元电路 - 变换电路